# THE DATASHEET OF FPGA

<u>Unit B, 13/F, Shing Lee Commercial Building</u> <u>No.8 Wing Kut Street, Central HK</u>

# Stratix II Device Handbook, Volume 1

101 Innovation Drive San Jose, CA 95134 www.altera.com

SII5V1-4.5

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

# Contents

| Chapter Revision Dates | vii |

|------------------------|-----|

|                        |     |

| About this Handbook    | i   |

| How to Contact Altera   | . i |

|-------------------------|-----|

| Typographic Conventions | . i |

## Section I. Stratix II Device Family Data Sheet

| Revision History | 7 Section I–1 |

|------------------|---------------|

|------------------|---------------|

### **Chapter 1. Introduction**

| Introduction              | 1–1   |

|---------------------------|-------|

| Features                  | 1 - 1 |

| Document Revision History | 1–6   |

### **Chapter 2. Stratix II Architecture**

| Functional Description          |  |

|---------------------------------|--|

| Logic Array Blocks              |  |

| LAB Interconnects               |  |

| LAB Control Signals             |  |

| Adaptive Logic Modules          |  |

| ALM Operating Modes             |  |

| Register Chain                  |  |

| Clear & Preset Logic Control    |  |

| MultiTrack Interconnect         |  |

| TriMatrix Memory                |  |

| Memory Block Size               |  |

| Digital Signal Processing Block |  |

| Modes of Operation              |  |

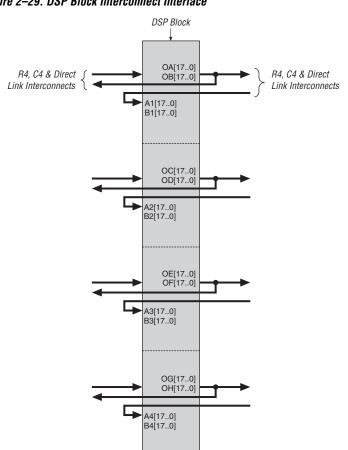

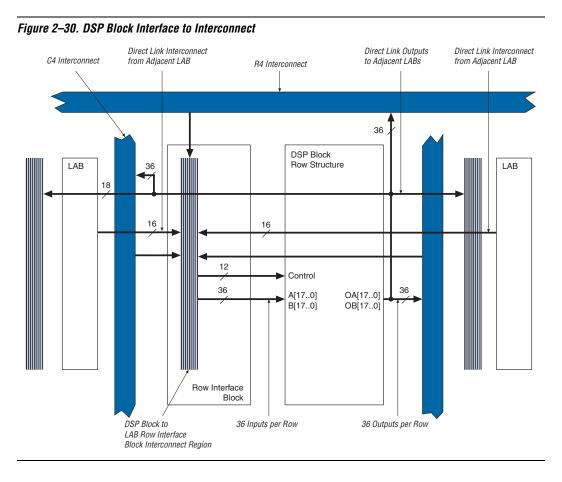

| DSP Block Interface             |  |

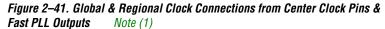

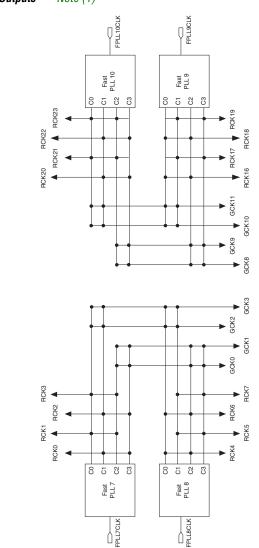

| PLLs & Clock Networks           |  |

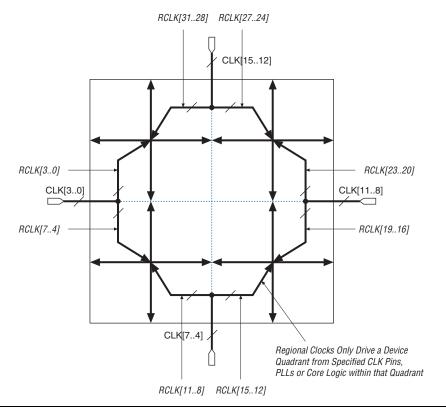

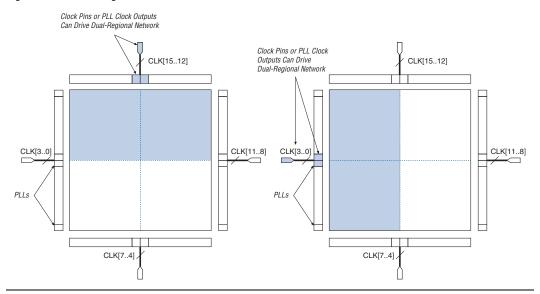

| Global & Hierarchical Clocking  |  |

| Enhanced & Fast PLLs            |  |

| Enhanced PLLs                   |  |

| Fast PLLs                       |  |

| I/O Structure                   |  |

| Double Data Rate I/O Pins       |  |

| External RAM Interfacing        |  |

| Programmable Drive Strength     |  |

| Open-Drain Output                            | 2–84 |

|----------------------------------------------|------|

| Bus Hold                                     |      |

| Programmable Pull-Up Resistor                | 2–85 |

| Advanced I/O Standard Support                |      |

| On-Chip Termination                          |      |

| MultiVolt I/O Interface                      | 2–93 |

| High-Speed Differential I/O with DPA Support | 2–96 |

| Dedicated Circuitry with DPA Support         |      |

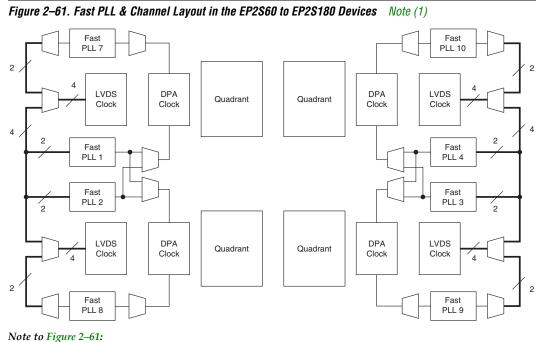

| Fast PLL & Channel Layout                    |      |

| Document Revision History                    |      |

|                                              |      |

|                                              |      |

### **Chapter 3. Configuration & Testing**

| IEEE Std. 1149.1 JTAG Boundary-Scan Support               | 3–1  |

|-----------------------------------------------------------|------|

| SignalTap II Embedded Logic Analyzer                      | 3–4  |

| Configuration                                             | 3–4  |

| Operating Modes                                           |      |

| Configuration Schemes                                     |      |

| Configuring Stratix II FPGAs with JRunner                 | 3–10 |

| Programming Serial Configuration Devices with SRunner     |      |

| Configuring Stratix II FPGAs with the MicroBlaster Driver | 3–11 |

| PLL Reconfiguration                                       | 3–11 |

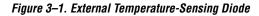

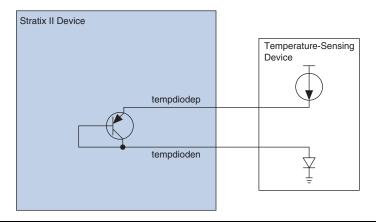

| Temperature Sensing Diode (TSD)                           | 3–11 |

| Automated Single Event Upset (SEU) Detection              | 3–13 |

| Custom-Built Circuitry                                    | 3–14 |

| Software Interface                                        |      |

| Document Revision History                                 | 3–14 |

|                                                           |      |

### Chapter 4. Hot Socketing & Power-On Reset

| Hot-Socketing Specifications 4-1                                                                        |

|---------------------------------------------------------------------------------------------------------|

| Devices Can Be Driven Before Power-Up 4-2                                                               |

| I/O Pins Remain Tri-Stated During Power-Up 4-2                                                          |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> , V <sub>CCINT</sub> or V <sub>CCPD</sub> Power Supplies |

| Hot Socketing Feature Implementation in Stratix II Devices                                              |

| Power-On Reset Circuitry                                                                                |

| Document Revision History 4-6                                                                           |

### **Chapter 5. DC & Switching Characteristics**

| Operating Conditions               | 5–1 |

|------------------------------------|-----|

| Absolute Maximum Ratings           | 5–1 |

| Recommended Operating Conditions   |     |

| DC Electrical Characteristics      | 5–3 |

| I/O Standard Specifications        | 5–4 |

| Bus Hold Specifications            |     |

| On-Chip Termination Specifications |     |

| Pin Capacitance                    |     |

| Power Consumption                  |     |

### EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

#### Contents

| 20         |

|------------|

| 20         |

| 21         |

| 27         |

| 34         |

| <b>1</b> 1 |

| 50         |

| 51         |

| 52         |

| 54         |

| 56         |

| 77         |

| 78         |

| 37         |

| 91         |

| 94         |

| 96         |

| 97         |

|            |

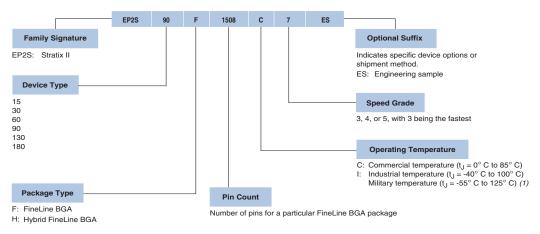

### Chapter 6. Reference & Ordering Information

| Software                  | 6–1 |

|---------------------------|-----|

| Device Pin-Outs           | 6–1 |

| Ordering Information      | 6–1 |

| Document Revision History |     |

Contents

### EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

# **Chapter Revision Dates**

The chapters in this book, *Stratix II Device Handbook, Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

| Chapter 1. | Introduction<br>Revised:<br>Part number:        |                  |

|------------|-------------------------------------------------|------------------|

| Chapter 2. | Stratix II Archit                               | ecture           |

| 1          | Revised:                                        | May 2007         |

|            | Part number:                                    |                  |

| Chapter 3  | <ol> <li>Configuration &amp; Testing</li> </ol> |                  |

| chapter 5. | Revised:                                        |                  |

|            | Part number:                                    |                  |

| Chapter 4. | Hot Socketing                                   | & Power-On Reset |

| Chapter 4. | Revised:                                        |                  |

|            | Part number:                                    |                  |

|            | i art number.                                   | 51151004-5.2     |

| Chapter 5. | DC & Switching Characteristics                  |                  |

| 1          | Revised:                                        |                  |

|            | Part number:                                    |                  |

| Chapter 6. | Reference & Ordering Information                |                  |

| enapter 0. | Revised:                                        |                  |

|            | Part number:                                    | ,                |

|            | i uni mumber.                                   | 01101000 2.2     |

**Chapter Revision Dates**

Stratix II Device Handbook, Volume 1

# About this Handbook

This handbook provides comprehensive information about the Altera® Stratix<sup>®</sup> II family of devices.

### How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method          | Address                   |

|---------------------------------|----------------------------|---------------------------|

| Technical support               | Website                    | www.altera.com/support    |

| Technical training              | Website www.altera.com/tra |                           |

|                                 | Email                      | custrain@altera.com       |

| Product literature              | Email                      | www.altera.com/literature |

| Altera literature services      | Website                    | literature@altera.com     |

| Non-technical support (General) | Email                      | nacomp@altera.com         |

| (Software Licensing)            | Email                      | authorization@altera.com  |

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

### Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                             |

### EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

### **Typographic Conventions**

#### Stratix II Device Handbook, Volume 1

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{P A}$ , $n + 1$ .                                                                                                                                                                                                                      |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <i><file name=""></file></i> , <i><project name="">.pof</project></i> file.                                                                                                                                                      |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| ••                                  | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| $\checkmark$                        | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

| L.                                  | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                             | The caution indicates required information that needs special consideration and<br>understanding and should be read prior to starting or continuing with the<br>procedure or process.                                                                                                                                   |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

|                                     | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

## Section I. Stratix II Device Family Data Sheet

This section provides the data sheet specifications for Stratix<sup>®</sup> II devices. This section contains feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix II devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix II Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, Hot Socketing & Power-On Reset

- Chapter 5, DC & Switching Characteristics

- Chapter 6, Reference & Ordering Information

### **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook. Stratix II Device Family Data Sheet

Stratix II Device Handbook, Volume 1

### EP2S180F1020C5N Intel IC FPGA 742 I/O 1020FBGA

### 1. Introduction

SII51001-4.2

### Introduction

The Stratix<sup>®</sup> II FPGA family is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). Stratix II devices offer up to 9 Mbits of on-chip, TriMatrix<sup>TM</sup> memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit × 18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. Various high-speed external memory interfaces are supported, including double data rate (DDR) SDRAM and DDR2 SDRAM, RLDRAM II, quad data rate (QDR) II SRAM, and single data rate (SDR) SDRAM. Stratix II devices support various I/O standards along with support for 1-gigabit per second (Gbps) source synchronous signaling with DPA circuitry. Stratix II devices offer a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs). Stratix II devices are also the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm to protect designs.

### Features

The Stratix II family offers the following features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

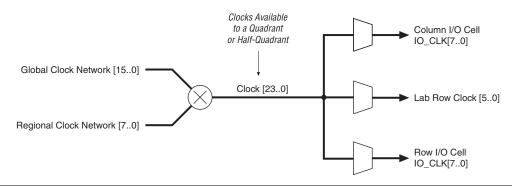

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

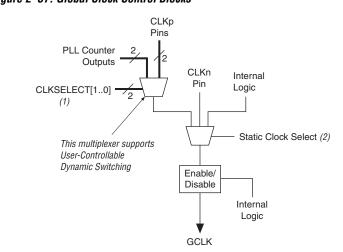

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support with DPA circuitry for 1-Gbps performance

- Support for high-speed networking and communications bus standards including Parallel RapidIO, SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport<sup>™</sup> technology, and SFI-4

- Support for high-speed external memory, including DDR and DDR2 SDRAM, RLDRAM II, QDR II SRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

| Table 1–1. Stratix II FPGA Family Features |         |           |           |           |           |           |  |  |  |

|--------------------------------------------|---------|-----------|-----------|-----------|-----------|-----------|--|--|--|

| Feature                                    | EP2\$15 | EP2\$30   | EP2\$60   | EP2S90    | EP2\$130  | EP2S180   |  |  |  |

| ALMs                                       | 6,240   | 13,552    | 24,176    | 36,384    | 53,016    | 71,760    |  |  |  |

| Adaptive look-up tables (ALUTs) (1)        | 12,480  | 27,104    | 48,352    | 72,768    | 106,032   | 143,520   |  |  |  |

| Equivalent LEs (2)                         | 15,600  | 33,880    | 60,440    | 90,960    | 132,540   | 179,400   |  |  |  |

| M512 RAM blocks                            | 104     | 202       | 329       | 488       | 699       | 930       |  |  |  |

| M4K RAM blocks                             | 78      | 144       | 255       | 408       | 609       | 768       |  |  |  |

| M-RAM blocks                               | 0       | 1         | 2         | 4         | 6         | 9         |  |  |  |

| Total RAM bits                             | 419,328 | 1,369,728 | 2,544,192 | 4,520,488 | 6,747,840 | 9,383,040 |  |  |  |

| DSP blocks                                 | 12      | 16        | 36        | 48        | 63        | 96        |  |  |  |

| 18-bit × 18-bit multipliers (3)            | 48      | 64        | 144       | 192       | 252       | 384       |  |  |  |

| Enhanced PLLs                              | 2       | 2         | 4         | 4         | 4         | 4         |  |  |  |

| Fast PLLs                                  | 4       | 4         | 8         | 8         | 8         | 8         |  |  |  |

| Maximum user I/O pins                      | 366     | 500       | 718       | 902       | 1,126     | 1,170     |  |  |  |

Notes to Table 1–1:

(1) One ALM contains two ALUTs. The ALUT is the cell used in the Quartus® II software for logic synthesis.

(2) This is the equivalent number of LEs in a Stratix device (four-input LUT-based architecture).

(3) These multipliers are implemented using the DSP blocks.

Stratix II devices are available in space-saving FineLine BGA<sup>®</sup> packages (see Tables 1–2 and 1–3).

| Table 1–2. Stratix II Package Options & I/O Pin Counts       Notes (1), (2) |                         |                                      |                            |                            |                           |                           |  |  |

|-----------------------------------------------------------------------------|-------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|--|--|

| Device                                                                      | 484-Pin<br>FineLine BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |  |  |

| EP2S15                                                                      | 342                     |                                      | 366                        |                            |                           |                           |  |  |

| EP2S30                                                                      | 342                     |                                      | 500                        |                            |                           |                           |  |  |

| EP2S60 (3)                                                                  | 334                     |                                      | 492                        |                            | 718                       |                           |  |  |

| EP2S90 (3)                                                                  |                         | 308                                  |                            | 534                        | 758                       | 902                       |  |  |

| EP2S130 (3)                                                                 |                         |                                      |                            | 534                        | 742                       | 1,126                     |  |  |

| EP2S180 (3)                                                                 |                         |                                      |                            |                            | 742                       | 1,170                     |  |  |

#### Notes to Table 1–2:

All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk1p, and clk11n) that can be used for data inputs.

(2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as generalpurpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

(3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes                                                              |                                                                                                                |      |      |      |       |       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------|--|--|--|--|

| Dimension         484 Pin         484-Pin         672 Pin         780 Pin         1,020 Pin         1,508 Pin |                                                                                                                |      |      |      |       |       |  |  |  |  |

| Pitch (mm)                                                                                                    | 1.00                                                                                                           | 1.00 | 1.00 | 1.00 | 1.00  | 1.00  |  |  |  |  |

| Area (mm2)                                                                                                    | 529                                                                                                            | 729  | 729  | 841  | 1,089 | 1,600 |  |  |  |  |

| Length × width<br>(mm × mm)                                                                                   | Length × width         23 × 23         27 × 27         27 × 27         29 × 29         33 × 33         40 × 40 |      |      |      |       |       |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

After compilation, check the information messages for a full list of I/O, DQ, LVDS, and other pins that are not available because of the selected migration path.

Table 1–4 lists the Stratix II device package offerings and shows the total number of non-migratable user I/O pins when migrating from one density device to a larger density device. Additional I/O pins may not be migratable if migrating from the larger device to the smaller density device.

When moving from one density to a larger density, the larger density device may have fewer user I/O pins. The larger device requires more power and ground pins to support the additional logic within the device. Use the Quartus II Pin Planner to determine which user I/O pins are migratable between the two devices.

. . . . . . . . . .

| Table 1–4. Total Number of Non-Migratable I/O Pins for Stratix II Vertical Migration Paths |                         |                         |       |    |                          |  |  |

|--------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|----|--------------------------|--|--|

| Vertical Migration<br>Path                                                                 | 484-Pin<br>FineLine BGA | 672-Pin<br>FineLine BGA |       |    | 1508-Pin<br>FineLine BGA |  |  |

| EP2S15 to EP2S30                                                                           | 0 (1)                   | 0                       |       |    |                          |  |  |

| EP2S15 to EP2S60                                                                           | 8 (1)                   | 0                       |       |    |                          |  |  |

| EP2S30 to EP2S60                                                                           | 8 (1)                   | 8                       |       |    |                          |  |  |

| EP2S60 to EP2S90                                                                           |                         |                         |       | 0  |                          |  |  |

| EP2S60 to EP2S130                                                                          |                         |                         |       | 0  |                          |  |  |

| EP2S60 to EP2S180                                                                          |                         |                         |       | 0  |                          |  |  |

| EP2S90 to EP2S130                                                                          |                         |                         | 0 (1) | 16 | 17                       |  |  |

| EP2S90 to EP2S180                                                                          |                         |                         |       | 16 | 0                        |  |  |

| EP2S130 to EP2S180                                                                         |                         |                         |       | 0  | 0                        |  |  |

Note to Table 1–4:

Some of the DQ/DQS pins are not migratable. Refer to the Quartus II software information messages for more detailed information.

To determine if your user I/O assignments are correct, run the I/O Assignment Analysis command in the Quartus II software (Processing > Start > Start I/O Assignment Analysis).

Refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook* for more information on pin migration.

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1–5 shows Stratix II device speed-grade offerings.

| Table 1–5 | Table 1–5. Stratix II Device Speed Grades |                            |                                      |                            |                            |                              |                              |  |  |

|-----------|-------------------------------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|

| Device    | Temperature<br>Grade                      | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |

| EP2S15    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |

| EP2S30    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |

| EP2S60    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            | -4                           |                              |  |  |

| EP2S90    | Commercial                                |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

| EP2S130   | Commercial                                |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

| EP2S180   | Commercial                                |                            |                                      |                            |                            | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

### Document Revision History

Table 1–6 shows the revision history for this chapter.

| Table 1–6. Docu                 | Table 1–6. Document Revision History                                                                                |                    |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| Date and<br>Document<br>Version | Changes Made                                                                                                        | Summary of Changes |  |  |  |  |

| May 2007, v4.2                  | Moved Document Revision History to the end of the chapter.                                                          | _                  |  |  |  |  |

| April 2006, v4.1                | <ul> <li>Updated "Features" section.</li> <li>Removed Note 4 from Table 1–2.</li> <li>Updated Table 1–4.</li> </ul> | _                  |  |  |  |  |

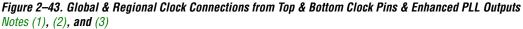

| December 2005,<br>v4.0          | <ul> <li>Updated Tables 1–2, 1–4, and 1–5.</li> <li>Updated Figure 2–43.</li> </ul>                                 | _                  |  |  |  |  |

| July 2005, v3.1                 | <ul> <li>Added vertical migration information, including<br/>Table 1–4.</li> <li>Updated Table 1–5.</li> </ul>      | _                  |  |  |  |  |

| May 2005, v3.0                  | <ul><li>Updated "Features" section.</li><li>Updated Table 1–2.</li></ul>                                            | _                  |  |  |  |  |

| March 2005,<br>v2.1             | Updated "Introduction" and "Features" sections.                                                                     | _                  |  |  |  |  |

| January 2005,<br>v2.0           | Added note to Table 1–2.                                                                                            | _                  |  |  |  |  |

| October 2004,<br>v1.2           | Updated Tables 1-2, 1-3, and 1-5.                                                                                   | _                  |  |  |  |  |

| July 2004, v1.1                 | <ul> <li>Updated Tables 1–1 and 1–2.</li> <li>Updated "Features" section.</li> </ul>                                | _                  |  |  |  |  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                   | _                  |  |  |  |  |

### 2. Stratix II Architecture

SII51002-4.3

# Functional Description

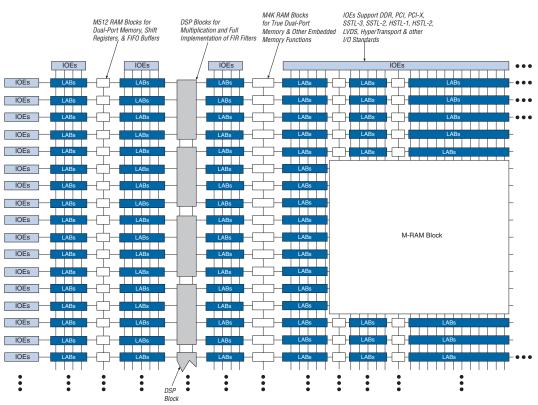

Stratix<sup>®</sup> II devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provides signal interconnects between logic array blocks (LABs), memory block structures (M512 RAM, M4K RAM, and M-RAM blocks), and digital signal processing (DSP) blocks.

Each LAB consists of eight adaptive logic modules (ALMs). An ALM is the Stratix II device family's basic building block of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

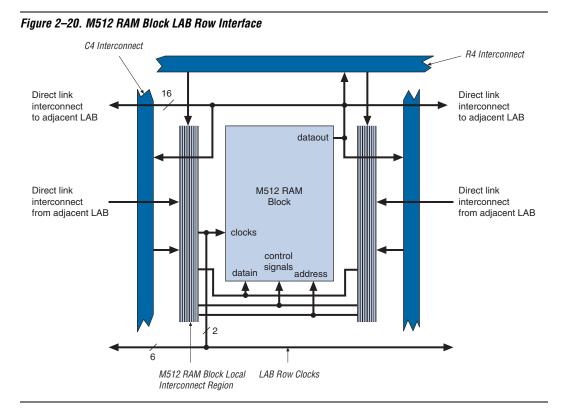

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 500 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

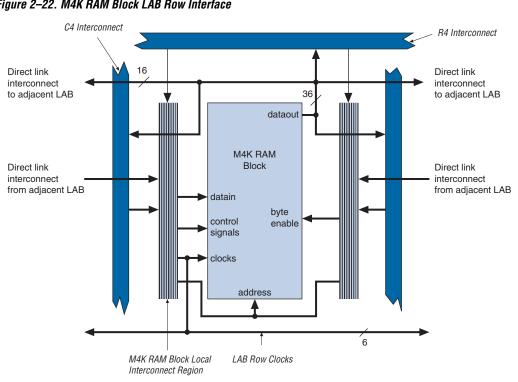

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 550 MHz. These blocks are grouped into columns across the device in between certain LABs.

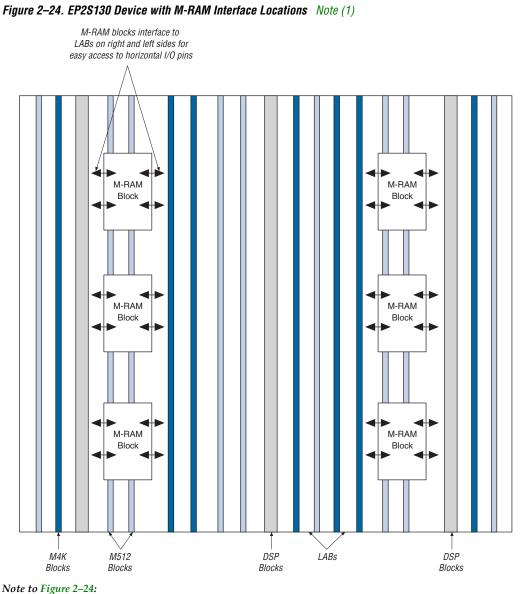

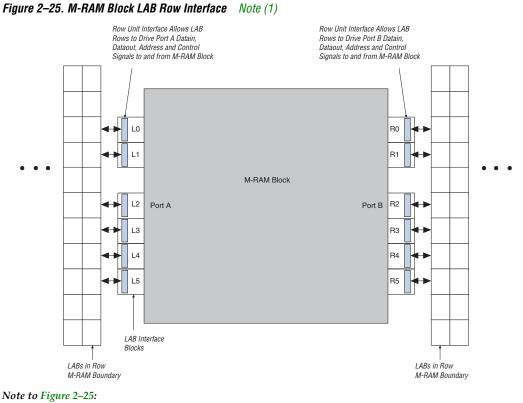

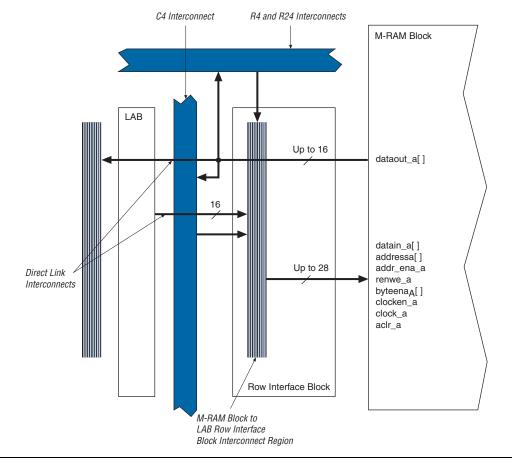

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 420 MHz. Several M-RAM blocks are located individually in the device's logic array.

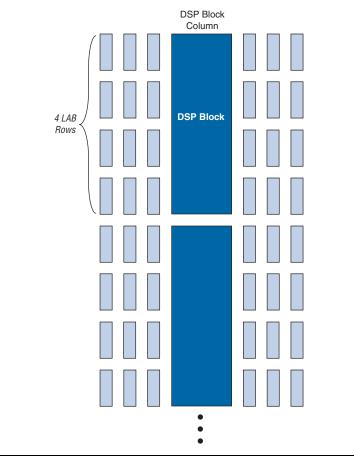

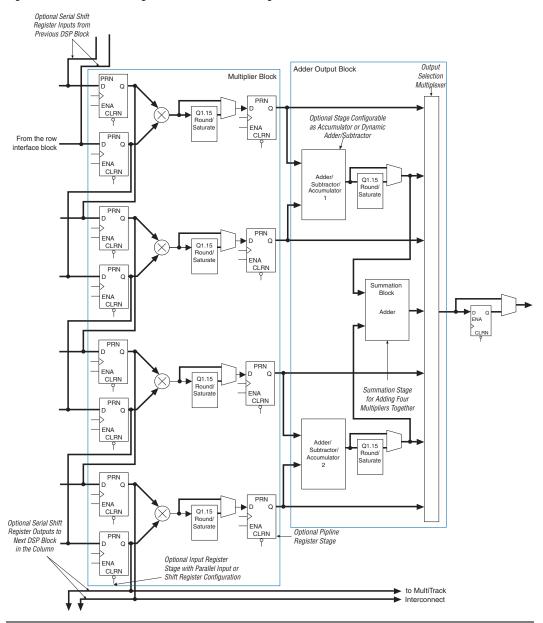

DSP blocks can implement up to either eight full-precision  $9 \times 9$ -bit multipliers, four full-precision  $18 \times 18$ -bit multipliers, or one full-precision  $36 \times 36$ -bit multiplier with add or subtract features. The DSP blocks support Q1.15 format rounding and saturation in the multiplier and accumulator stages. These blocks also contain shift registers for digital signal processing applications, including finite impulse response (FIR) and infinite impulse response (IIR) filters. DSP blocks are grouped into columns across the device and operate at up to 450 MHz.

#### **Functional Description**

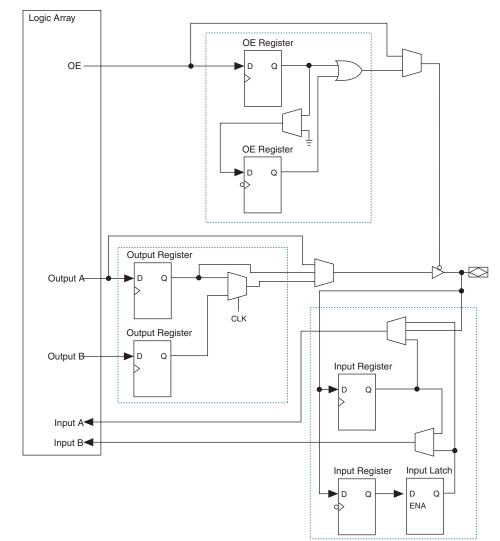

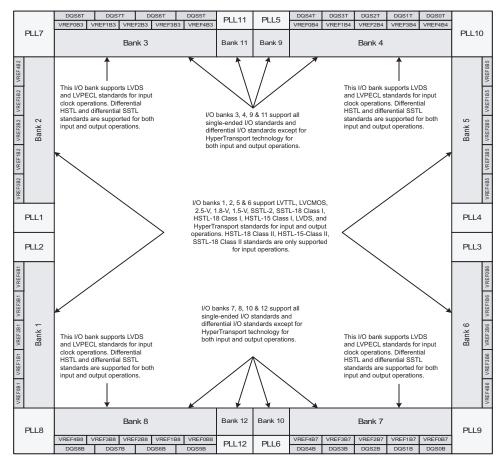

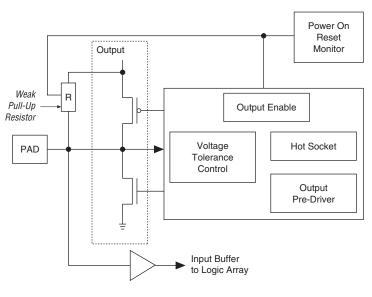

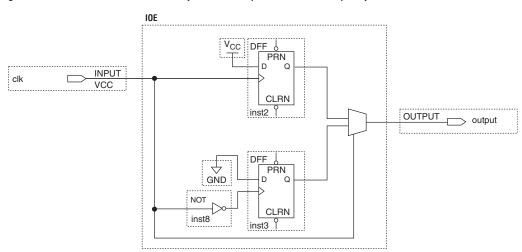

Each Stratix II device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR and DDR2 SDRAM, RLDRAM II, and QDR II SRAM devices. High-speed serial interface channels with dynamic phase alignment (DPA) support data transfer at up to 1 Gbps using LVDS or HyperTransport<sup>™</sup> technology I/O standards.

#### Figure 2–1 shows an overview of the Stratix II device.

Figure 2–1. Stratix II Block Diagram

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix II devices.

| Table 2–1. Stratix II Device Resources |                            |                           |                 |                             |                |          |  |  |  |

|----------------------------------------|----------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|--|--|--|

| Device                                 | M512 RAM<br>Columns/Blocks | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |  |  |  |

| EP2S15                                 | 4 / 104                    | 3 / 78                    | 0               | 2 / 12                      | 30             | 26       |  |  |  |

| EP2S30                                 | 6 / 202                    | 4 / 144                   | 1               | 2 / 16                      | 49             | 36       |  |  |  |

| EP2S60                                 | 7 / 329                    | 5 / 255                   | 2               | 3 / 36                      | 62             | 51       |  |  |  |

| EP2S90                                 | 8 / 488                    | 6 / 408                   | 4               | 3 / 48                      | 71             | 68       |  |  |  |

| EP2S130                                | 9 / 699                    | 7 / 609                   | 6               | 3 / 63                      | 81             | 87       |  |  |  |

| EP2S180                                | 11 / 930                   | 8 / 768                   | 9               | 4 / 96                      | 100            | 96       |  |  |  |

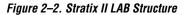

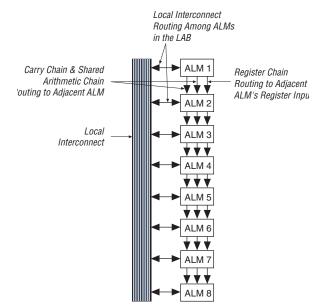

### Logic Array Blocks

Each LAB consists of eight ALMs, carry chains, shared arithmetic chains, LAB control signals, local interconnect, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. Register chain connections transfer the output of an ALM register to the adjacent ALM register in an LAB. The Quartus<sup>®</sup> II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix II LAB structure.

#### Logic Array Blocks

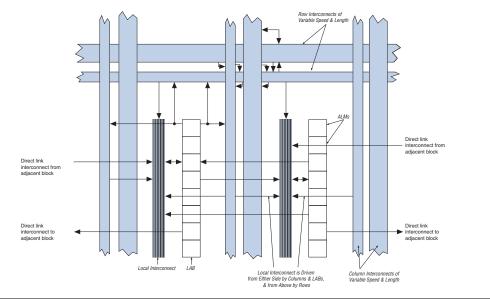

### **LAB Interconnects**

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

Stratix II Architecture

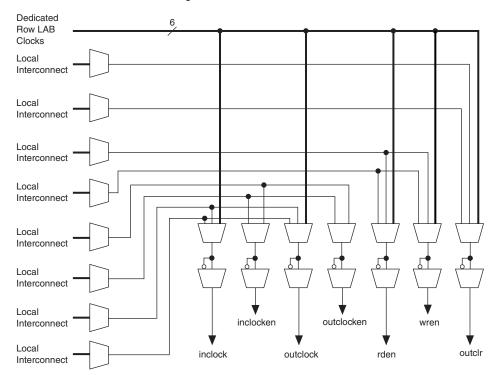

### **LAB Control Signals**

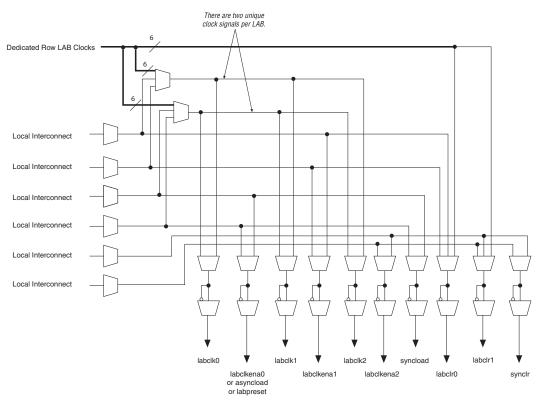

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals. This gives a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–4. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-up option or assign a given register to power up high using the Quartus II software, the preset is achieved using the asynchronous load

#### Adaptive Logic Modules

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

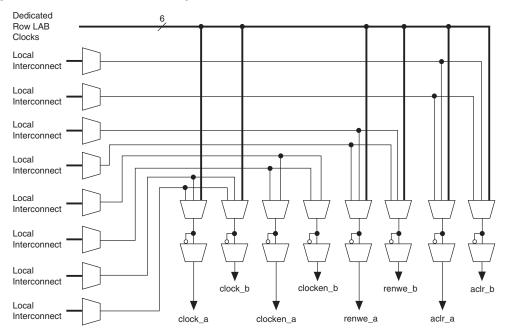

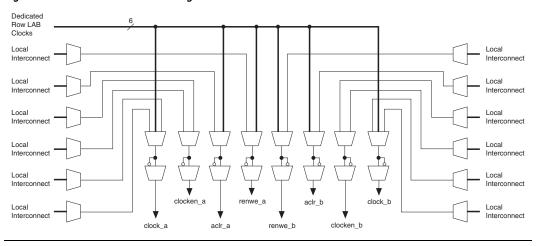

The LAB row clocks [5...0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>™</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2–4. LAB-Wide Control Signals

### Adaptive Logic Modules

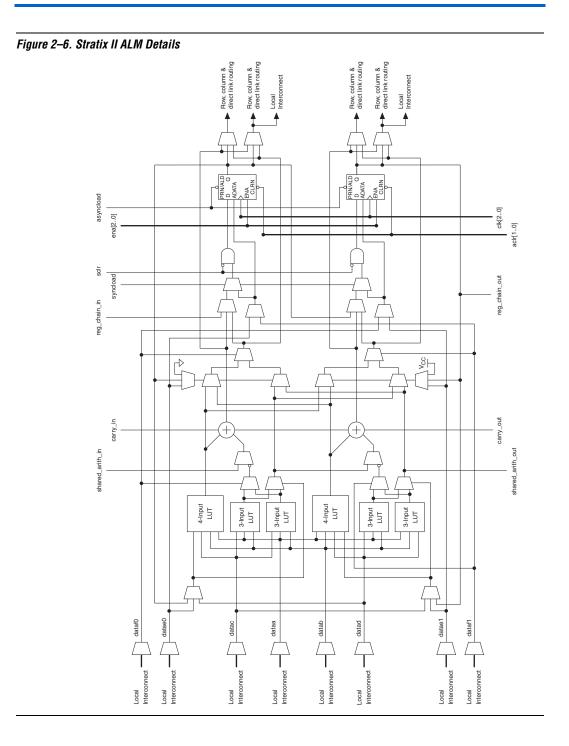

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–5 shows a high-level block diagram of the Stratix II ALM while Figure 2–6 shows a detailed view of all the connections in the ALM.

#### Adaptive Logic Modules

One ALM contains two programmable registers. Each register has data, clock, clock enable, synchronous and asynchronous clear, asynchronous load data, and synchronous and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous load data. The asynchronous load data input comes from the datae or dataf input of the ALM, which are the same inputs that can be used for register packing. For combinational functions, the register is bypassed and the output of the LUT drives directly to the outputs of the ALM.

Each ALM has two sets of outputs that drive the local, row, and column routing resources. The LUT, adder, or register output can drive these output drivers independently (see Figure 2–6). For each set of output drivers, two ALM outputs can drive column, row, or direct link routing connections, and one of these ALM outputs can also drive local interconnect resources. This allows the LUT or adder to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the combinational logic for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same ALM so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The ALM can also drive out registered and unregistered versions of the LUT or adder output.

••••

See the *Performance & Logic Efficiency Analysis of Stratix II Devices White Paper* for more information on the efficiencies of the Stratix II ALM and comparisons with previous architectures.

### **ALM Operating Modes**

The Stratix II ALM can operate in one of the following modes:

- Normal mode

- Extended LUT mode

- Arithmetic mode

- Shared arithmetic mode

Each mode uses ALM resources differently. In each mode, eleven available inputs to the ALM--the eight data inputs from the LAB local interconnect; carry-in from the previous ALM or LAB; the shared arithmetic chain connection from the previous ALM or LAB; and the register chain connection--are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset/load, synchronous clear, synchronous load, and clock enable control for the register. These LABwide signals are available in all ALM modes. See the "LAB Control Signals" section for more information on the LAB-wide control signals.

The Quartus II software and supported third-party synthesis tools, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically choose the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which ALM operating mode to use for optimal performance.

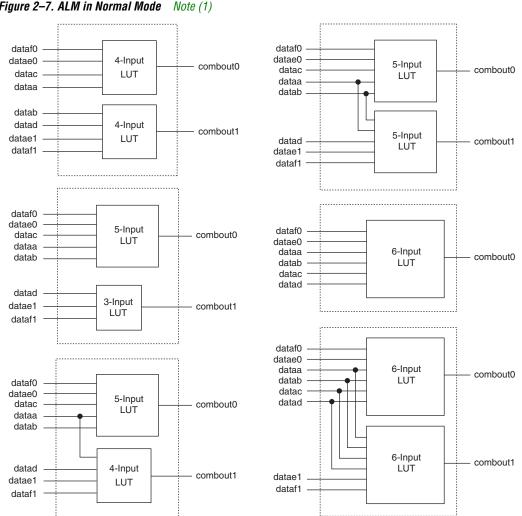

### Normal Mode

The normal mode is suitable for general logic applications and combinational functions. In this mode, up to eight data inputs from the LAB local interconnect are inputs to the combinational logic. The normal mode allows two functions to be implemented in one Stratix II ALM, or an ALM to implement a single function of up to six inputs. The ALM can support certain combinations of completely independent functions and various combinations of functions which have common inputs. Figure 2–7 shows the supported LUT combinations in normal mode.

Stratix II Architecture

#### Figure 2-7. ALM in Normal Mode

#### Note to Figure 2–7:

(1)Combinations of functions with fewer inputs than those shown are also supported. For example, combinations of functions with the following number of inputs are supported: 4 and 3, 3 and 3, 3 and 2, 5 and 2, etc.

> The normal mode provides complete backward compatibility with fourinput LUT architectures. Two independent functions of four inputs or less can be implemented in one Stratix II ALM. In addition, a five-input function and an independent three-input function can be implemented without sharing inputs.

#### **Adaptive Logic Modules**

For the packing of two five-input functions into one ALM, the functions must have at least two common inputs. The common inputs are dataa and datab. The combination of a four-input function with a five-input function requires one common input (either dataa or datab).

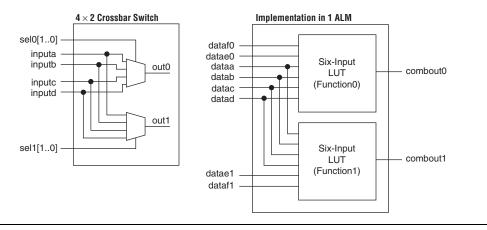

In the case of implementing two six-input functions in one ALM, four inputs must be shared and the combinational function must be the same. For example, a 4 × 2 crossbar switch (two 4-to-1 multiplexers with common inputs and unique select lines) can be implemented in one ALM, as shown in Figure 2–8. The shared inputs are dataa, datab, datac, and datad, while the unique select lines are datae0 and dataf0 for function0, and datae1 and dataf1 for function1. This crossbar switch consumes four LUTs in a four-input LUT-based architecture.

#### Figure 2–8. 4 × 2 Crossbar Switch Example

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

Any six-input function can be implemented utilizing inputs dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized, the output is driven to register0, and/or register0 is bypassed and the data drives out to the interconnect using the top set of output drivers (see Figure 2–9). If

datael and datafl are utilized, the output drives to registerl and/or bypasses registerl and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

#### Notes to Figure 2–9:

- If datael and datafl are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

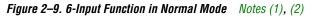

### Extended LUT Mode

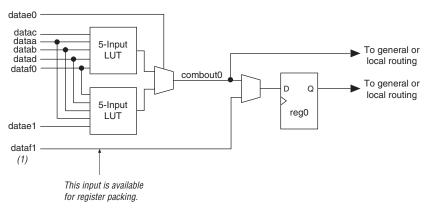

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

#### Note to Figure 2–10:

(1) If the seven-input function is unregistered, the unused eighth input is available for register packing. The second register, reg1, is not available.

#### Arithmetic Mode

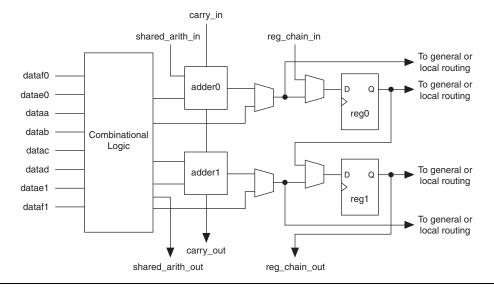

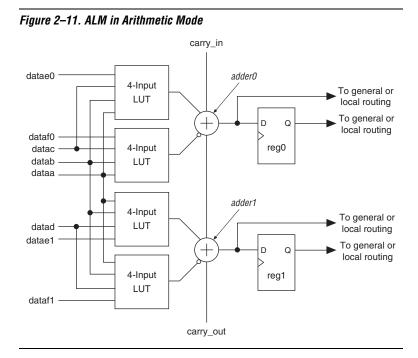

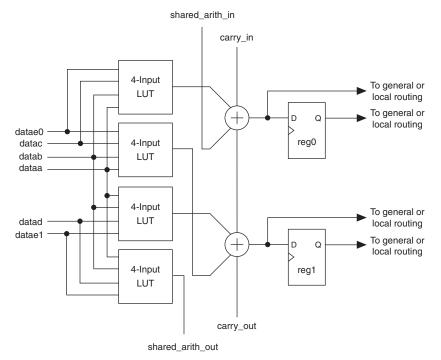

The arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An ALM in arithmetic mode uses two sets of two four-input LUTs along with two dedicated full adders. The dedicated adders allow the LUTs to be available to perform pre-adder logic; therefore, each adder can add the output of two four-input functions. The four LUTs share the dataa and datab inputs. As shown in Figure 2–11, the carry-in signal feeds to adder0, and the carry-out from adder0 feeds to carry-in of adder1. The carry-out from adder1 drives to adder0 of the next ALM in the LAB. ALMs in arithmetic mode can drive out registered and/or unregistered versions of the adder outputs.

Stratix II Architecture

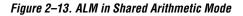

While operating in arithmetic mode, the ALM can support simultaneous use of the adder's carry output along with combinational logic outputs. In this operation, the adder output is ignored. This usage of the adder with the combinational logic output provides resource savings of up to 50% for functions that can use this ability. An example of such functionality is a conditional operation, such as the one shown in Figure 2–12. The equation for this example is:

$$R = (X < Y) ? Y : X$$

To implement this function, the adder is used to subtract 'Y' from 'X.' If 'X' is less than 'Y,' the carry\_out signal is '1.' The carry\_out signal is fed to an adder where it drives out to the LAB local interconnect. It then feeds to the LAB-wide syncload signal. When asserted, syncload selects the syncdata input. In this case, the data 'Y' drives the syncdata inputs to the registers. If 'X' is greater than or equal to 'Y,' the syncload signal is de-asserted and 'X' drives the data port of the registers.

Figure 2–12. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up/down control, add/subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up/down and add/subtract control signals. These control signals are good candidates for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

#### **Carry Chain**

The carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in an LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects. The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column.

To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. This leaves the other half of the ALMs in the LAB available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB carry into the bottom half of the ALMs in the next LAB within the column. Every other column of LABs is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on carry chain interconnect.

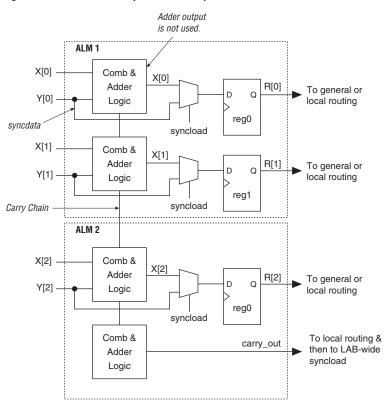

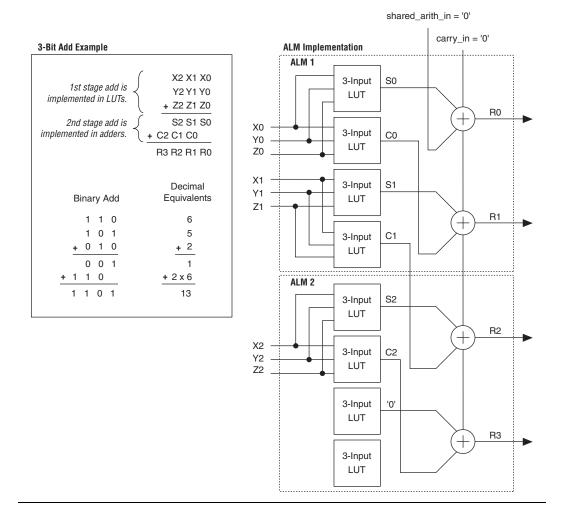

#### Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) via a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure 2–13 shows the ALM in shared arithmetic mode.

#### Adaptive Logic Modules

#### Note to Figure 2–13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

Stratix II Architecture

#### Figure 2–14. Example of a 3-bit Add Utilizing Shared Arithmetic Mode

#### Shared Arithmetic Chain

In addition to the dedicated carry chain routing, the shared arithmetic chain available in shared arithmetic mode allows the ALM to implement a three-input add. This significantly reduces the resources necessary to implement large adder trees or correlator functions.

The shared arithmetic chains can begin in either the first or fifth ALM in an LAB. The Quartus II Compiler creates shared arithmetic chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long shared

#### **Adaptive Logic Modules**

arithmetic chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A shared arithmetic chain can continue as far as a full column.

Similar to the carry chains, the shared arithmetic chains are also top- or bottom-half bypassable. This capability allows the shared arithmetic chain to cascade through half of the ALMs in a LAB while leaving the other half available for narrower fan-in functionality. Every other LAB column is top-half bypassable, while the other LAB columns are bottomhalf bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on shared arithmetic chain interconnect.

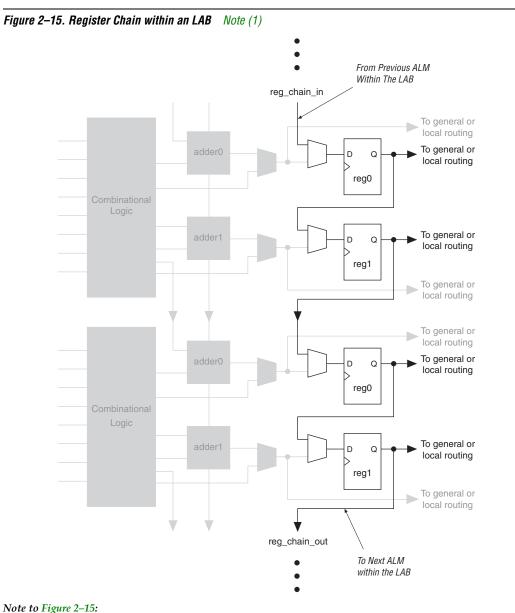

# **Register Chain**

In addition to the general routing outputs, the ALMs in an LAB have register chain outputs. The register chain routing allows registers in the same LAB to be cascaded together. The register chain interconnect allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between ALMs while saving local interconnect resources (see Figure 2–15). The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance.

Stratix II Architecture

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

# **Clear & Preset Logic Control**

|                            | LAB-wide signals control the logic for the register's clear and load/preset<br>signals. The ALM directly supports an asynchronous clear and preset<br>function. The register preset is achieved through the asynchronous load<br>of a logic high. The direct asynchronous preset does not require a NOT-<br>gate push-back technique. Stratix II devices support simultaneous<br>asynchronous load/preset, and clear signals. An asynchronous clear<br>signal takes precedence if both signals are asserted simultaneously. Each<br>LAB supports up to two clears and one load/preset signal.<br>In addition to the clear and load/preset ports, Stratix II devices provide a<br>device-wide reset pin (DEV_CLRn) that resets all registers in the device.<br>An option set before compilation in the Quartus II software controls this<br>pin. This device-wide reset overrides all other control signals. |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MultiTrack<br>Interconnect | In the Stratix II architecture, connections between ALMs, TriMatrix<br>memory, DSP blocks, and device I/O pins are provided by the MultiTrack<br>interconnect structure with DirectDrive™ technology. The MultiTrack<br>interconnect consists of continuous, performance-optimized routing lines<br>of different lengths and speeds used for inter- and intra-design block<br>connectivity. The Quartus II Compiler automatically places critical design<br>paths on faster interconnects to improve design performance.                                                                                                                                                                                                                                                                                                                                                                                    |

|                            | DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                            | The MultiTrack interconnect consists of row and column interconnects<br>that span fixed distances. A routing structure with fixed length resources<br>for all devices allows predictable and repeatable performance when<br>migrating through different device densities. Dedicated row<br>interconnects route signals to and from LABs, DSP blocks, and TriMatrix<br>memory in the same row. These row resources include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            | <ul> <li>Direct link interconnects between LABs and adjacent blocks</li> <li>R4 interconnects traversing four blocks to the right or left</li> <li>R24 row interconnects for high-speed access across the length of the device</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

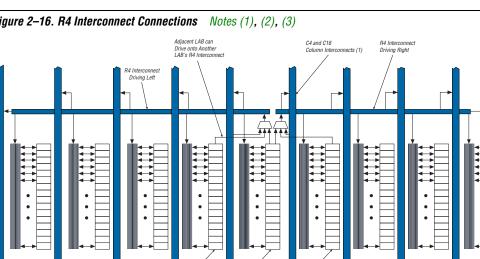

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

I AB

Neighbo

Primari

LAB (2)

#### Notes to Figure 2–16:

- (1)C4 and C16 interconnects can drive R4 interconnects.

- (2)This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

I AR

Neighbo

#### MultiTrack Interconnect

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and Row IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect. These column resources include:

- Shared arithmetic chain interconnects in an LAB

- Carry chain interconnects in an LAB and from LAB to LAB

- Register chain interconnects in an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix II devices include an enhanced interconnect structure in LABs for routing shared arithmetic chains and carry chains for efficient arithmetic functions. The register chain connection allows the register output of one ALM to connect directly to the register input of the next ALM in the LAB for fast shift registers. These ALM to ALM connections bypass the local interconnect. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–17 shows the shared arithmetic chain, carry chain and register chain interconnects.

# Figure 2–17. Shared Arithmetic Chain, Carry Chain & Register Chain Interconnects

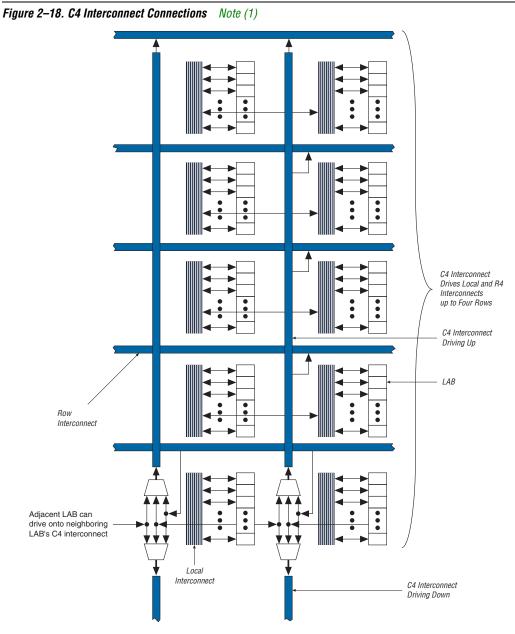

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–18 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

#### MultiTrack Interconnect

### Note to Figure 2–18:

(1) Each C4 interconnect can drive either up or down four rows.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LABto-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk[5..0].

Table 2–2 shows the Stratix II device's routing scheme.

| Table 2–2. Stratix II Device Routing Scheme (Part 1 of 2) |                         |             |                |                    |                          |                 |                  |                 |                  |              |                |               |             |            |              |              |

|-----------------------------------------------------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|--------------|----------------|---------------|-------------|------------|--------------|--------------|

|                                                           |                         |             |                |                    |                          | Destination     |                  |                 |                  |              |                |               |             |            |              |              |

| Source                                                    | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM          | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E   | Row IOE      |

| Shared arithmetic chain                                   |                         |             |                |                    |                          |                 |                  |                 |                  | $\checkmark$ |                |               |             |            |              |              |

| Carry chain                                               |                         |             |                |                    |                          |                 |                  |                 |                  | >            |                |               |             |            |              |              |

| Register chain                                            |                         |             |                |                    |                          |                 |                  |                 |                  | >            |                |               |             |            |              |              |

| Local interconnect                                        |                         |             |                |                    |                          |                 |                  |                 |                  | $\checkmark$ | $\checkmark$   | $\checkmark$  | >           | >          | $\checkmark$ | $\checkmark$ |

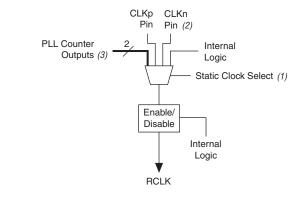

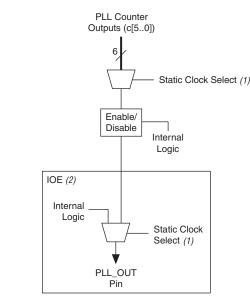

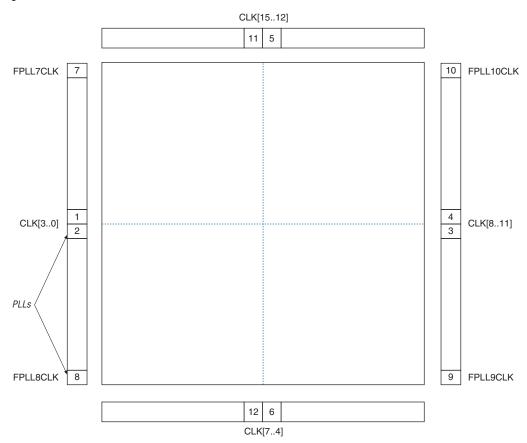

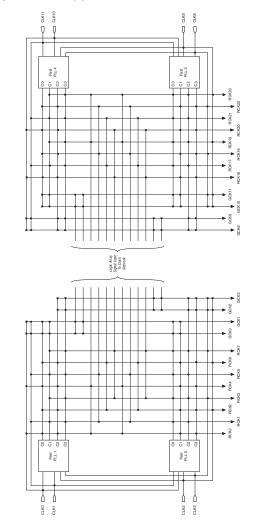

| Direct link interconnect                                  |                         |             |                | >                  |                          |                 |                  |                 |                  |              |                |               |             |            |              |              |