# THE DATASHEET OF FPGA

<u>+00852-56412601</u> <u>(\$\square\$ +00852-56412601</u>

Ounit B, 13/F, Shing Lee Commercial Building No.8 Wing Kut Street, Central HK

## 1. Stratix III Device Family Overview

SIII51001-1.8

The Stratix<sup>®</sup> III family provides one of the most architecturally advanced, high-performance, low-power FPGAs in the marketplace.

Stratix III FPGAs lower power consumption through Altera's innovative Programmable Power Technology, which provides the ability to turn on the performance where needed and turn down the power consumption for blocks not in use. Selectable Core Voltage and the latest in silicon process optimizations are also employed to deliver the industry's lowest power, high-performance FPGAs.

Specifically designed for ease of use and rapid system integration, the Stratix III FPGA family offers two variants optimized to meet different application needs:

- The Stratix III *L* family provides balanced logic, memory, and multiplier ratios for mainstream applications.

- The Stratix III *E* family is memory- and multiplier-rich for data-centric applications.

Modular I/O banks with a common bank structure for vertical migration lend efficiency and flexibility to the high-speed I/O. Package and die enhancements with dynamic on-chip termination, output delay, and current strength control provide best-in-class signal integrity.

Based on a 1.1-V, 65-nm all-layer copper SRAM process, the Stratix III family is a programmable alternative to custom ASICs and programmable processors for high-performance logic, digital signal processing (DSP), and embedded designs.

Stratix III devices include optional configuration bit stream security through volatile or non-volatile 256-bit Advanced Encryption Standard (AES) encryption. Where ultra-high reliability is required, Stratix III devices include automatic error detection circuitry to detect data corruption by soft errors in the configuration random-access memory (CRAM) and user memory cells.

### **Features Summary**

Stratix III devices offer the following features:

- 48,000 to 338,000 equivalent logic elements (LEs) ( refer to Table 1–1)

- 2,430 to 20,497 Kbits of enhanced TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and FIFO buffers

- High-speed DSP blocks provide dedicated implementation of 9×9, 12×12, 18×18, and 36×36 multipliers (at up to 550 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- I/O:GND:PWR ratio of 8:1:1 along with on-die and on-package decoupling for robust signal integrity

- Programmable Power Technology, which minimizes power while maximizing device performance

- Selectable Core Voltage, available in low-voltage devices (L ordering code suffix), enables selection of lowest power or highest performance operation

- Up to 16 global clocks, 88 regional clocks, and 116 peripheral clocks per device

- Up to 12 phase-locked loops (PLLs) per device that support PLL reconfiguration, clock switchover, programmable bandwidth, clock synthesis, and dynamic phase shifting

- Memory interface support with dedicated DQS logic on all I/O banks

- Support for high-speed external memory interfaces including DDR, DDR2, DDR3 SDRAM, RLDRAM II, QDR II, and QDR II+ SRAM on up to 24 modular I/O banks

- Up to 1,104 user I/O pins arranged in 24 modular I/O banks that support a wide range of industry I/O standards

- Dynamic On-Chip Termination (OCT) with auto calibration support on all I/O banks

- High-speed differential I/O support with serializer/deserializer (SERDES) and dynamic phase alignment (DPA) circuitry for 1.6 Gbps performance

- Support for high-speed networking and communications bus standards including SPI-4.2, SFI-4, SGMII, Utopia IV, 10 Gigabit Ethernet XSBI, Rapid I/O, and NPSI

- The only high-density, high-performance FPGA with support for 256-bit AES volatile and non-volatile security key to protect designs

- Robust on-chip hot socketing and power sequencing support

- Integrated cyclical redundancy check (CRC) for configuration memory error detection with critical error determination for high availability systems support

- Built-in error correction coding (ECC) circuitry to detect and correct data errors in M144K TriMatrix memory blocks

- Nios® II embedded processor support

- Support for multiple intellectual property megafunctions from Altera® MegaCore® functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>)

Features Summary

#### Table 1–1 lists the Stratix III FPGA family features.

Table 1-1. FPGA Family Features for Stratix III Devices

|                         | Device/<br>Feature | ALMs | LEs    | M9K<br>Blocks | M144K<br>Blocks | MLAB<br>Blocks | Total<br>Embedded<br>RAM Kbits | MLAB<br>RAM<br>Kbits | Total<br>RAM<br>Kbits(2) | 18×18-bit<br>Multipliers<br>(FIR Mode) | PLLs (3) |

|-------------------------|--------------------|------|--------|---------------|-----------------|----------------|--------------------------------|----------------------|--------------------------|----------------------------------------|----------|

|                         | EP3SL50            | 19K  | 47.5K  | 108           | 6               | 950            | 1,836                          | 297                  | 2,133                    | 216                                    | 4        |

|                         | EP3SL70            | 27K  | 67.5K  | 150           | 6               | 1,350          | 2,214                          | 422                  | 2,636                    | 288                                    | 4        |

| Stratix III             | EP3SL110           | 43K  | 107.5K | 275           | 12              | 2,150          | 4,203                          | 672                  | 4,875                    | 288                                    | 8        |

| Logic<br>Family         | EP3SL150           | 57K  | 142.5K | 355           | 16              | 2,850          | 5,499                          | 891                  | 6,390                    | 384                                    | 8        |

| ,                       | EP3SL200           | 80K  | 200K   | 468           | 36              | 4,000          | 9,396                          | 1,250                | 10,646                   | 576                                    | 12       |

|                         | EP3SL340           | 135K | 337.5K | 1,040         | 48              | 6,750          | 16,272                         | 2,109                | 18,381                   | 576                                    | 12       |

|                         | EP3SE50            | 19K  | 47.5K  | 400           | 12              | 950            | 5,328                          | 297                  | 5,625                    | 384                                    | 4        |

| Stratix III<br>Enhanced | EP3SE80            | 32K  | 80K    | 495           | 12              | 1,600          | 6,183                          | 500                  | 6,683                    | 672                                    | 8        |

| Family                  | EP3SE110           | 43K  | 107.5K | 639           | 16              | 2,150          | 8,055                          | 672                  | 8,727                    | 896                                    | 8        |

|                         | EP3SE260           | 102K | 255K   | 864           | 48              | 5,100          | 14,688                         | 1,594                | 16,282                   | 768                                    | 12       |

#### Notes to Table 1-1:

- (1) MLAB ROM mode supports twice the number of MLAB RAM Kbits.

- (2) For total ROM Kbits, use this equation to calculate: Total ROM Kbits = Total Embedded RAM Kbits + [(# of MLAB blocks × 640)/1024]

- (3) The availability of the PLLs shown in this column is based on the device with the largest package. Refer to the Clock Networks and PLLs in Stratix III Devices chapter in volume 1 of the Stratix III Device Handbook for the availability of the PLLs for each device.

The Stratix III logic family (*L*) offers balanced logic, memory, and multipliers to address a wide range of applications, while the enhanced family (*E*) offers more memory and multipliers per logic and is ideal for wireless, medical imaging, and military applications.

Stratix III devices are available in space-saving FineLine BGA (FBGA) packages (refer to Table 1–2 and Table 1–3).

**Table 1–2.** Package Options and I/O Pin Counts (Note 1)

| Device   | 484-Pin<br>FineLine<br>BGA (2) | 780-Pin<br>FineLine<br>BGA (2) | 1152-Pin<br>FineLine<br>BGA (2) | 1517-Pin<br>FineLine BGA<br>(3) | 1760-Pin<br>FineLine BGA<br>(3) |

|----------|--------------------------------|--------------------------------|---------------------------------|---------------------------------|---------------------------------|

| EP3SL50  | <b>1</b> 296                   | 488                            | _                               | _                               | _                               |

| EP3SL70  | 296                            | 488                            | _                               | _                               | _                               |

| EP3SL110 | _                              | 488                            | <b>1</b> 744                    | _                               | _                               |

| EP3SL150 | _                              | 488                            | 744                             | _                               | _                               |

| EP3SL200 | _                              | 488 (5)                        | 744                             | 976                             | _                               |

| EP3SL340 |                                | _                              | 744 (4)                         | 976                             | 1,120                           |

| EP3SE50  | 296                            | 488                            | _                               | <u> </u>                        | _                               |

| EP3SE80  | _                              | 488                            | 744                             |                                 | _                               |

| EP3SE110 | _                              | 488                            | 744                             | _                               | _                               |

| EP3SE260 | _                              | 488 (5)                        | 744                             | 976                             | _                               |

#### Notes to Table 1-2:

- (1) The arrows indicate vertical migration.

- (2) All I/O pin counts include eight dedicated clock inputs (CLK1p, CLK1n, CLK3p, CLK3n, CLK8p, CLK8n, CLK10p, and CLK10n) that can be used for data inputs.

- (3) All I/O pin counts include eight dedicated clock inputs (CLK1p, CLK1n, CLK3p, CLK3n, CLK8p, CLK8n, CLK10p, and CLK10n) and eight dedicated corner PLL clock inputs (PLL\_L1\_CLKp, PLL\_L1\_CLKn, PLL\_L4\_CLKp, PLL\_L4\_CLKn, PLL\_R4\_CLKp, PLL\_R4\_CLKp, PLL\_R4\_CLKp, PLL\_R1\_CLKp, and PLL\_R1\_CLKn) that can be used for data inputs.

- (4) The EP3SL340 FPGA is offered only in the H1152 package, but not offered in the F1152 package.

- (5) The EP3SE260 and EP3SL200 FPGAs are offered only in the H780 package, but not offered in the F780 package.

All Stratix III devices support vertical migration within the same package (for example, you can migrate between the EP3SL50 and EP3SL70 devices in the 780-pin FineLine BGA package). Vertical migration allows you to migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus® II software. On the Assignments menu, point to **Device** and click **Migration Devices**. You can migrate from the L family to the E family without increasing the number of LEs available. This minimizes the cost of vertical migration.

Table 1–3 lists the Stratix III FineLine BGA (FBGA) package sizes.

Table 1-3. FineLine BGA Package Sizes

| Dimension            | 484 Pin | 780 Pin | 1152 Pin | 1517 Pin | 1760 Pin |

|----------------------|---------|---------|----------|----------|----------|

| Pitch (mm)           | 1.00    | 1.00    | 1.00     | 1.00     | 1.00     |

| Area (mm²)           | 529     | 841     | 1,225    | 1,600    | 1,849    |

| Length/Width (mm/mm) | 23/23   | 29/29   | 35/35    | 40/40    | 43/43    |

Table 1–4 lists the Stratix III Hybrid FineLine BGA (HBGA) package sizes.

Table 1-4. Hybrid FineLine BGA Package Sizes

| Dimension            | 780 Pin | 1152 Pin |

|----------------------|---------|----------|

| Pitch (mm)           | 1.00    | 1.00     |

| Area (mm²)           | 1,089   | 1,600    |

| Length/Width (mm/mm) | 33/33   | 40/40    |

Stratix III devices are available in up to three speed grades: –2, –3, and –4, with –2 being the fastest. Stratix III devices are offered in both commercial and industrial temperature range ratings with leaded and lead-free packages. Selectable Core Voltage is available in specially marked low-voltage devices (*L* ordering code suffix).

Table 1–5 lists the Stratix III device speed grades.

**Table 1–5.** Speed Grades for Stratix III Devices (Part 1 of 2)

| Device    | Temperature<br>Grade | 484 -Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 780-Pin<br>Hybrid<br>FineLine<br>BGA | 1152-Pin<br>FineLine<br>BGA | 1152-Pin<br>Hybrid<br>FineLine<br>BGA | 1517-Pin<br>FineLine<br>BGA | 1760-Pin<br>FineLine<br>BGA |

|-----------|----------------------|-----------------------------|----------------------------|--------------------------------------|-----------------------------|---------------------------------------|-----------------------------|-----------------------------|

| EP3SL50   | Commercial           | -2, -3, -4,<br>-4L          | -2, -3,-4,<br>-4L          | _                                    | _                           | _                                     | _                           | _                           |

|           | Industrial           | -3, -4, -4L                 | -3, -4, -4L                | _                                    | _                           | _                                     | _                           | _                           |

| EP3SL70   | Commercial           | -2, -3, -4,<br>-4L          | -2, -3, -4,<br>-4L         | _                                    | _                           | _                                     | _                           | _                           |

|           | Industrial           | -3, -4, -4L                 | -3, -4, -4L                |                                      |                             |                                       |                             |                             |

| EP3SL110  | Commercial           | 1                           | -2, -3, -4,<br>-4L         |                                      | -2, -3, -4,<br>-4L          |                                       |                             |                             |

|           | Industrial           |                             | -3, -4, -4L                | 1                                    | -3, -4, -4L                 | 1                                     | 1                           | 1                           |

| EP3SL150  | Commercial           | 1                           | -2,-3, -4,<br>-4L          |                                      | -2, -3, -4,<br>-4L          |                                       |                             |                             |

|           | Industrial           | _                           | -3, -4, -4L                | _                                    | -3, -4, -4L                 | _                                     | _                           | _                           |

| EP3SL200  | Commercial           | 1                           | 1                          | -2,-3, -4,<br>-4L                    | -2,-3, -4,<br>-4L           | -                                     | -2,-3, -4,<br>-4L           |                             |

|           | Industrial (1)       |                             |                            | −3, −4, −4L                          | −3, −4, −4L                 | 1                                     | -3, -4, -4L                 | 1                           |

| EP3SL340  | Commercial           |                             |                            |                                      | -                           |                                       | -2, -3, -4                  |                             |

| LI OOLO40 | Industrial (1)       | _                           |                            | _                                    | _                           | −3, −4, −4L                           | -3, -4, -4L                 | −3, −4, −4L                 |

| EP3SE50   | Commercial           | -2, -3, -4,<br>-4L          | -2, -3, -4,<br>-4L         | -                                    | -                           | -                                     | -                           | -                           |

|           | Industrial           | -3, -4, -4L                 | -3, -4, -4L                | _                                    | _                           | _                                     | _                           | _                           |

| EP3SE80   | Commercial           | _                           | -2, -3, -4,<br>-4L         | 1                                    | -2, -3, -4,<br>-4L          | 1                                     | _                           | _                           |

|           | Industrial           | _                           | -3, -4, -4L                |                                      | -3, -4, -4L                 |                                       |                             |                             |

| EP3SE110  | Commercial           | _                           | -2,-3, -4,<br>-4L          | _                                    | -2, -3, -4,<br>-4L          | _                                     | _                           | _                           |

|           | Industrial           |                             | -3, -4, -4L                | _                                    | -3, -4, -4L                 | _                                     | _                           | _                           |

| <b>Table 1–5.</b> S | Speed Grades | for Stratix III Device | s (Part 2 of 2) |

|---------------------|--------------|------------------------|-----------------|

|---------------------|--------------|------------------------|-----------------|

| Device   | Temperature<br>Grade | 484 -Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 780-Pin<br>Hybrid<br>FineLine<br>BGA | 1152-Pin<br>FineLine<br>BGA | 1152-Pin<br>Hybrid<br>FineLine<br>BGA | 1517-Pin<br>FineLine<br>BGA | 1760-Pin<br>FineLine<br>BGA |

|----------|----------------------|-----------------------------|----------------------------|--------------------------------------|-----------------------------|---------------------------------------|-----------------------------|-----------------------------|

| EP3SE260 | Commercial           | _                           | _                          | -2, -3, -4,<br>-4L                   | -2,- 3, -4,<br>-4L          | _                                     | -2, -3, -4,<br>-4L          | _                           |

|          | Industrial (1)       |                             |                            | -3, -4, -4L                          | -3, -4, -4L                 | _                                     | -3, -4,-4L                  | _                           |

#### Note to Table 1-5:

#### Architecture Features

The following section describes the various features of the Stratix III family FPGAs.

### **Logic Array Blocks and Adaptive Logic Modules**

The Logic Array Block (LAB) is composed of basic building blocks known as Adaptive Logic Modules (ALMs) that can be configured to implement logic, arithmetic, and register functions. Each LAB consists of ten ALMs, carry chains, shared arithmetic chains, LAB control signals, local interconnect, and register chain connection lines. ALMs are part of a unique, innovative logic structure that delivers faster performance, minimizes area, and reduces power consumption. ALMs expand the traditional 4-input look-up table architecture to 7 inputs, increasing performance by reducing LEs, logic levels, and associated routing. In addition, ALMs maximize DSP performance with dedicated functionality to efficiently implement adder trees and other complex arithmetic functions. The Quartus II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency.

The Stratix III LAB has a new derivative called Memory LAB (or MLAB), which adds SRAM memory capability to the LAB. MLAB is a superset of the LAB and includes all LAB features. MLABs support a maximum of 320 bits of simple dual-port Static Random Access Memory (SRAM). Each ALM in an MLAB can be configured as a  $16\times2$  block, resulting in a configuration of  $16\times20$  simple dual port SRAM block. MLAB and LAB blocks always co-exist as pairs in all Stratix III families, allowing up to 50% of the logic (LABs) to be traded for memory (MLABs).

For more information about LABs and ALMs, refer to the *Logic Array Blocks and Adaptive Logic Modules in Stratix III Devices* chapter.

For more information about MLAB modes, features and design considerations, refer to the *TriMatrix Embedded Memory Blocks in Stratix III Devices* chapter.

<sup>(1)</sup> For EP3SL340, EP3SL200, and EP3SE260 devices, the industrial junction temperature range for -4L is 0-100°C, regardless of supply voltage.

#### **MultiTrack Interconnect**

In the Stratix III architecture, connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. The MultiTrack interconnect provides 1-hop connection to 34 adjacent LABs, 2-hop connections to 96 adjacent LABs and 3-hop connections to 160 adjacent LABs.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the reoptimization cycles that typically follow design changes and additions. The Quartus II Compiler also automatically places critical design paths on faster interconnects to improve design performance.

For more information, refer to the *MultiTrack Interconnect in Stratix III Devices* chapter.

### **TriMatrix Embedded Memory Blocks**

TriMatrix embedded memory blocks provide three different sizes of embedded SRAM to efficiently address the needs of Stratix III FPGA designs. TriMatrix memory includes the following blocks:

- 320-bit MLAB blocks optimized to implement filter delay lines, small FIFO buffers, and shift registers

- 9-Kbit M9K blocks that can be used for general purpose memory applications

- 144-Kbit M144K blocks that are ideal for processor code storage, packet and video frame buffering

Each embedded memory block can be independently configured to be a single- or dual-port RAM, ROM, or shift register via the Quartus II MegaWizard™ Plug-In Manager. Multiple blocks of the same type can also be stitched together to produce larger memories with minimal timing penalty. TriMatrix memory provides up to 16,272 Kbits of embedded SRAM at up to 600 MHz operation.

For more information about TriMatrix memory blocks, modes, features, and design considerations, refer to the *TriMatrix Embedded Memory Blocks in Stratix III Devices* chapter.

#### **DSP Blocks**

Stratix III devices have dedicated high-performance digital signal processing (DSP) blocks optimized for DSP applications requiring high data throughput. Stratix III devices provide you with the ability to implement various high-performance DSP functions easily. Complex systems such as WiMAX, 3GPP WCDMA, CDMA2000, voice over Internet Protocol (VoIP), H.264 video compression, and high-definition television (HDTV) require high-performance DSP blocks to process data. These system designs typically use DSP blocks to implement finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, and discrete cosine transform (DCT) functions.

Stratix III devices have up to 112 DSP blocks. The architectural highlights of the Stratix III DSP block are the following:

- High-performance, power optimized, fully pipelined multiplication operations

- Native support for 9-bit, 12-bit, 18-bit, and 36-bit word lengths

- Native support for 18-bit complex multiplications

- Efficient support for floating point arithmetic formats (24-bit for Single Precision and 53-bit for Double Precision)

- Signed and unsigned input support

- Built-in addition, subtraction, and accumulation units to efficiently combine multiplication results

- Cascading 18-bit input bus to form tap-delay lines

- Cascading 44-bit output bus to propagate output results from one block to the next block

- Rich and flexible arithmetic rounding and saturation units

- Efficient barrel shifter support

- Loopback capability to support adaptive filtering

DSP block multipliers can optionally feed an adder/subtractor or accumulator in the block depending on user configuration. This option saves ALM routing resources and increases performance, because all connections and blocks are inside the DSP block. Additionally, the DSP Block input registers can efficiently implement shift registers for FIR filter applications, and the Stratix III DSP blocks support rounding and saturation. The Quartus II software includes megafunctions that control the mode of operation of the DSP blocks based on user parameter settings.

For more information, refer to the *DSP Blocks in Stratix III Devices* chapter.

#### **Clock Networks and PLLs**

Stratix III devices provide dedicated Global Clock Networks (GCLKs), Regional Clock Networks (RCLKs), and Periphery Clock Networks (PCLKs). These clocks are organized into a hierarchical clock structure that provides up to 104 unique clock domains (16 GCLK + 88 RCLK) within the Stratix III device and allows for up to 38 (16 GCLK + 22 RCLK) unique GCLK/RCLK clock sources per device quadrant.

Stratix III devices deliver abundant PLL resources with up to 12 PLLs per device and up to 10 outputs per PLL. Every output can be independently programmed, creating a unique, customizable clock frequency. Inherent jitter filtration and fine granularity control over multiply, divide ratios, and dynamic phase-shift reconfiguration provide the high-performance precision required in today's high-speed applications. Stratix III PLLs are feature rich, supporting advanced capabilities such as clock switchover, reconfigurable phase shift, PLL reconfiguration, and reconfigurable bandwidth. PLLs can be used for general-purpose clock management supporting multiplication, phase shifting, and programmable duty cycle. Stratix III PLLs also support external feedback mode, spread-spectrum input clock tracking, and post-scale counter cascading.

For more information, refer to the *Clock Networks and PLLs in Stratix III Devices* chapter.

#### I/O Banks and I/O Structure

Stratix III devices contain up to 24 modular I/O banks, each of which contains 24, 32, 36, 40, or 48 I/Os. This modular bank structure improves pin efficiency and eases device migration. The I/O banks contain circuitry to support external memory interfaces at speeds up to 533 MHz and high-speed differential I/O interfaces meeting up to 1.6 Gbps performance. It also supports high-speed differential inputs and outputs running at speeds up to 800 MHz.

Stratix III devices support a wide range of industry I/O standards, including single-ended, voltage referenced single-ended, and differential I/O standards. The Stratix III I/O supports programmable bus hold, programmable pull-up resistor, programmable slew rate, programmable drive strength, programmable output delay control, and open-drain output. Stratix III devices also support on-chip series ( $R_s$ ) and on-chip parallel ( $R_T$ ) termination with auto calibration for single-ended I/O standards and on-chip differential termination ( $R_D$ ) for LVDS I/O standards on Left/Right I/O banks. Dynamic OCT is also supported on bi-directional I/O pins in all I/O banks.

For more information, refer to the *Stratix III Device I/O Features* chapter.

#### **External Memory Interfaces**

The Stratix III I/O structure has been completely redesigned to provide flexibility and enable high-performance support for existing and emerging external memory standards such as DDR, DDR2, DDR3, QDR II, QDR II+, and RLDRAM II at frequencies of up to 533 MHz.

Packed with features such as dynamic on-chip termination, trace mismatch compensation, read/write leveling, half-rate registers, and 4-to 36-bit programmable DQ group widths, Stratix III I/Os supply the built-in functionality required for rapid and robust implementation of external memory interfaces. Double data-rate support is found on all sides of the Stratix III device. Stratix III devices provide an efficient architecture to quickly and easily fit wide external memory interfaces exactly where you want them.

A self-calibrating soft IP core (ALTMEMPHY), optimized to take advantage of the Stratix III device I/O, along with the Quartus II timing analysis tool (TimeQuest), provide the total solution for the highest reliable frequency of operation across process voltage and temperature.

For more information about external memory interfaces, refer to the *External Memory Interfaces in Stratix III Devices* chapter.

### High-Speed Differential I/O Interfaces with DPA

Stratix III devices contain dedicated circuitry for supporting differential standards at speeds up to 1.6 Gbps. The high-speed differential I/O circuitry supports the following high-speed I/O interconnect standards and applications: Utopia IV, SPI-4.2, SFI-4, 10 Gigabit Ethernet XSBI, Rapid I/O, and NPSI. Stratix III devices support  $2\times$ ,  $4\times$ ,  $6\times$ ,  $7\times$ ,  $8\times$ , and  $10\times$  SERDES modes for high-speed differential I/O interfaces and

$4\times$ ,  $6\times$ ,  $7\times$ ,  $8\times$ , and  $10\times$  SERDES modes when using the dedicated DPA circuitry. DPA minimizes bit errors, simplifies PCB layout and timing management for high-speed data transfer, and eliminates channel-to-channel and channel-to-clock skew in high-speed data transmission systems. Soft CDR can also be implemented, enabling low-cost 1.6-Gbps clock embedded serial links.

Stratix III devices have the following dedicated circuitry for high-speed differential I/O support:

- Differential I/O buffer

- Transmitter serializer

- Receiver deserializer

- Data realignment

- Dynamic phase aligner (DPA)

- Soft CDR functionality

- Synchronizer (FIFO buffer)

- PLLs

- For more information, refer to the *High Speed Differential I/O Interfaces with DPA in Stratix III Devices* chapter.

#### **Hot Socketing and Power-On Reset**

Stratix III devices are hot-socketing compliant. Hot socketing is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. Robust on-chip hot-socketing and power-sequencing support ensures proper device operation independent of the power-up sequence. You can insert or remove a Stratix III board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot-socketing feature makes it easier to use Stratix III devices on PCBs that also contain a mixture of 3.3-V, 3.0-V, 2.5-V, 1.8-V, 1.5-V, and 1.2-V devices. With the Stratix III hot socketing feature, you do not need to ensure a specific power-up sequence for each device on the board.

For more information, refer to the *Hot Socketing and Power-On Reset in Stratix III Devices* chapter.

### Configuration

Stratix III devices are configured using one of the following four configuration schemes:

- Fast passive parallel (FPP)

- Fast active serial (AS)

- Passive serial (PS)

- Joint Test Action Group (JTAG)

All configuration schemes use either an external controller (for example, a MAX® II device or microprocessor), a configuration device, or a download cable.

Stratix III devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and transmit this compressed bitstream to Stratix III devices. During configuration, the Stratix III device decompresses the bitstream in real time and programs its SRAM cells.

Stratix III devices support decompression in the FPP when using a MAX II device/microprocessor plus flash, fast AS, and PS configuration schemes. The Stratix III decompression feature is not available in the FPP when using the enhanced configuration device and JTAG configuration schemes.

For more information, refer to the *Configuring Stratix III Devices* chapter.

#### **Remote System Upgrades**

Stratix III devices feature remote system upgrade capability, allowing error-free deployment of system upgrades from a remote location securely and reliably. Soft logic (either the Nios embedded processor or user logic) implemented in a Stratix III device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, and can recover from an error condition by reverting back to a safe configuration image, and provides error status information. This dedicated remote system upgrade circuitry is unique to Stratix series FPGAs and helps to avoid system downtime.

For more information, refer to the *Remote System Upgrades with Stratix III Devices* chapter.

### **IEEE 1149.1 (JTAG) Boundary-Scan Testing**

Stratix III devices support the JTAG IEEE Std. 1149.1 specification. The Boundary-Scan Test (BST) architecture offers the capability to test pin connections without using physical test probes and capture functional data while a device is operating normally. Boundary-scan cells in the Stratix III device can force signals onto pins or capture data from pin or logic array signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared to expected results. In addition to BST, you can use the IEEE Std. 1149.1 controller for Stratix III device in-circuit reconfiguration (ICR).

For more information, refer to the *IEEE 1149.1 (JTAG) Boundary Scan Testing in Stratix III Devices* chapter.

### **Design Security**

Stratix III devices are high-density, high-performance FPGAs with support for 256-bit volatile and non-volatile security keys to protect designs against copying, reverse engineering, and tampering. Stratix III devices have the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm, an industry standard encryption algorithm that is FIPS-197 certified and requires a 256-bit security key.

The design security feature is available when configuring Stratix III FPGAs using the fast passive parallel (FPP) configuration mode with an external host (such as a MAX II device or microprocessor), or when using fast active serial (AS) or passive serial (PS) configuration schemes.

For more information about the design security feature, refer to the *Design Security in Stratix III Devices* chapter.

#### **SEU Mitigation**

Stratix III devices have built-in error detection circuitry to detect data corruption due to soft errors in the configuration random-access memory (CRAM) cells. This feature allows all CRAM contents to be read and verified continuously during user mode operation to match a configuration-computed CRC value. The enhanced CRC circuit and frame-based configuration architecture allows detection and location of multiple, single, and adjacent bit errors which, in conjunction with a soft circuit supplied as a reference design, allows don't-care soft errors in the CRAM to be ignored during device operation. This provides a steep decrease in the effective soft error rate, increasing system reliability.

On-chip memory block SEU mitigation is also offered using the ninth bit and a configurable megafunction in the Quartus II software for MLAB and M9K blocks while the M144K memory blocks have built-in error correction code (ECC) circuitry.

For more information about the dedicated error detection circuitry, refer to the *SEU Mitigation in Stratix III Devices* chapter.

### **Programmable Power**

Stratix III delivers Programmable Power, the only FPGA with user programmable power options balancing today's power and performance requirements. Stratix III devices utilize the most advanced power-saving techniques, including a variety of process, circuit, and architecture optimizations and innovations. In addition, user controllable power reduction techniques provide an optimal balance of performance and power reduction specific for each design configured into the Stratix III FPGA. The Quartus II software (starting from version 6.1) automatically optimizes designs to meet the performance goals while simultaneously leveraging the programmable power-saving options available in the Stratix III FPGA without the need for any changes to the design flow.

For more information about Programmable Power in Stratix III devices, refer to the following documents:

- Programmable Power and Temperature Sensing Diode in Stratix III Devices chapter

- AN 437: Power Optimization in Stratix III FPGAs

- Stratix III Programmable Power White Paper

#### **Signal Integrity**

Stratix III devices simplify the challenge of signal integrity through a number of chip, package, and board level enhancements to enable efficient high-speed data transfer into and out of the device. These enhancements include:

- 8:1:1 user I/O/Gnd/V<sub>CC</sub> ratio to reduce the loop inductance in the package

- Dedicated power supply for each I/O bank, limit of I/Os is 24 to 48 I/Os per bank, to help limit simultaneous switching noise

- Programmable slew-rate support with up to four settings to match desired I/O standard, control noise, and overshoot

- Programmable output-current drive strength support with up to six settings to match desired I/O standard performance

- Programmable output-delay support to control rise/fall times and adjust duty cycle, compensate for skew, and reduce simultaneous switching outputs (SSO) noise

- Dynamic OCT with auto calibration support for series and parallel OCT and differential OCT support for LVDS I/O standard on the left/right banks

- For more information about SI support in the Quartus II software, refer to the *Quartus II Handbook*.

- For more information about how to use the various configuration, PLL, external memory interfaces, I/O, high-speed differential I/O, power, and JTAG pins, refer to the *Stratix III Device Family Pin Connection Guidelines*.

## **Reference and Ordering Information**

The following section describes Stratix III device software support and ordering information.

## **Software Support**

Stratix III devices are supported by the Altera Quartus II design software, version 6.1 and later, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, SignalTap® II logic analyzer, and device configuration.

The Quartus II software supports a variety of operating systems. The specific operating system for the Quartus II software can be obtained from the Quartus II **Readme.txt** file or the *Operating System Support* section of the Altera website. It also supports seamless integration with industry-leading EDA tools through the NativeLink® interface.

### **Ordering Information**

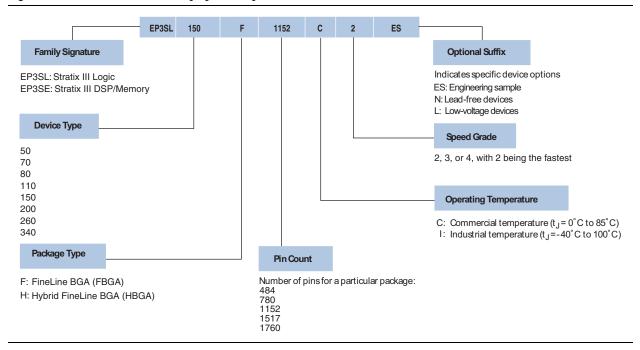

Figure 1–1 shows the ordering codes for Stratix III devices.

For more information about a specific package, refer to the *Stratix III Device Package Information* chapter.

Figure 1–1. Stratix III Device Packaging Ordering Information

## **Chapter Revision History**

Table 1–6 lists the revision history for this chapter.

**Table 1–6.** Chapter Revision History (Part 1 of 2)

| Date          | Version | Changes Made                                                     |

|---------------|---------|------------------------------------------------------------------|

|               |         | Updated for the Quartus II software version 9.1 SP2 release:     |

| March 2010    | 1.8     | ■ Updated Table 1–2.                                             |

|               |         | <ul><li>Updated "I/O Banks and I/O Structure" section.</li></ul> |

| May 2009      | 1.7     | Updated "Software" and "Signal Integrity" sections.              |

|               |         | <ul><li>Updated "Features" section.</li></ul>                    |

| February 2009 | 1.6     | ■ Updated Table 1–1.                                             |

|               |         | Removed "Referenced Documents" section.                          |

|               |         | <ul><li>Updated "Features" section.</li></ul>                    |

| October 2008  | 1.5     | ■ Updated Table 1–1 and Table 1–5.                               |

|               |         | <ul> <li>Updated New Document Format.</li> </ul>                 |

Table 1-6. Chapter Revision History (Part 2 of 2)

| Date          | Version | Changes Made                                                                              |

|---------------|---------|-------------------------------------------------------------------------------------------|

|               |         | <ul><li>Updated "Introduction".</li></ul>                                                 |

|               |         | ■ Updated Table 1–1.                                                                      |

| May 2000      | 1 4     | ■ Updated Table 1–2.                                                                      |

| May 2008      | 1.4     | Added Table 1–5.                                                                          |

|               |         | Updated "Reference and Ordering Information".                                             |

|               |         | ■ Updated package type information in Figure 1–1.                                         |

| November 2007 | 1.0     | ■ Updated Table 1–1.                                                                      |

| November 2007 | 1.3     | ■ Updated Table 1–2.                                                                      |

|               |         | Minor typo fixes.                                                                         |

| October 2007  | 4.0     | Added Table 1–4.                                                                          |

| October 2007  | 1.2     | Added section "Referenced Documents".                                                     |

|               |         | <ul> <li>Added live links for references.</li> </ul>                                      |

| May 2007      | 1.1     | Minor formatting changes, fixed PLL numbers and ALM, LE and MLAB bit counts in Table 1–1. |

| November 2006 | 1.0     | Initial Release.                                                                          |

Chapter 1: Stratix III Device Family Overview

Chapter Revision History

1–16

# THE DATASHEET OF FPGA

<u>+00852-56412601</u> <u>(\$\square\$ +00852-56412601</u>

Ounit B, 13/F, Shing Lee Commercial Building No.8 Wing Kut Street, Central HK