## THE DATASHEET OF FPGA

<u>+00852-56412601</u> <u>(\$\square\$ +00852-56412601</u>

Ounit B, 13/F, Shing Lee Commercial Building No.8 Wing Kut Street, Central HK

## Section I. HardCopy Stratix Device Family Data Sheet

This section provides designers with the data sheet specifications for HardCopy® Stratix structured ASICs. The chapters contain feature definitions of the internal architecture, JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, and a reference to power consumption for HardCopy Stratix structured ASICs.

This section contains the following:

- Chapter 1, Introduction to HardCopy Stratix Devices

- Chapter 2, Description, Architecture, and Features

- Chapter 3, Boundary-Scan Support

- Chapter 4, Operating Conditions

- Chapter 5, Quartus II Support for HardCopy Stratix Devices

- Chapter 6, Design Guidelines for HardCopy Stratix Performance Improvement

### **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section I-1

HardCopy Series Handbook, Volume 1

Section I–2 Altera Corporation

## 1. Introduction to HardCopy Stratix Devices

H51001-2.4

#### Introduction

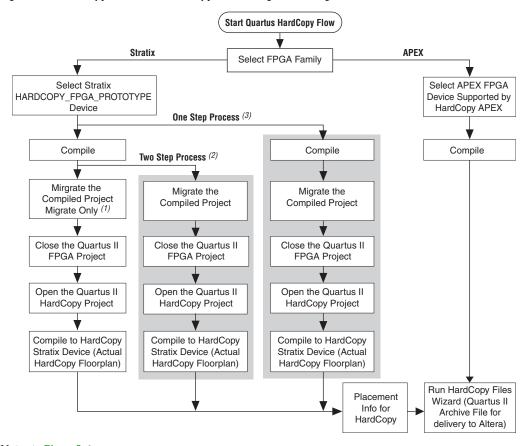

HardCopy® Stratix® structured ASICs, Altera's second-generation HardCopy structured ASICs, are low-cost, high-performance devices with the same architecture as the high-density Stratix FPGAs. The combination of Stratix FPGAs for prototyping and design verification, HardCopy Stratix devices for high-volume production, and the Quartus® II design software beginning with version 3.0, provide a complete and powerful alternative to ASIC design and development.

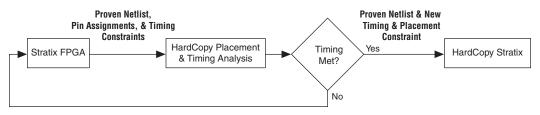

HardCopy Stratix devices are architecturally equivalent and have the same features as the corresponding Stratix FPGA. They offer pin-to-pin compatibility using the same package as the corresponding Stratix FPGA prototype. Designers can prototype their design to verify functionality with Stratix FPGAs before seamlessly migrating the proven design to a HardCopy Stratix structured ASIC.

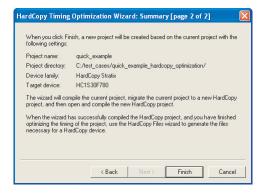

The Quartus II software provides a complete set of inexpensive and easy-to-use tools for designing HardCopy Stratix devices. Using the successful and proven methodology from HardCopy APEX™ devices, Stratix FPGA designs can be seamlessly and quickly migrated to a low-cost ASIC alternative. Designers can use the Quartus II software to design HardCopy Stratix devices to obtain an average of 50% higher performance and up to 40% lower power consumption than can be achieved in the corresponding Stratix FPGAs. The migration process is fully automated, requires minimal customer involvement, and takes approximately eight weeks to deliver fully tested HardCopy Stratix prototypes.

The HardCopy Stratix devices use the same base arrays across multiple designs for a given device density and are customized using the top two metal layers. The HardCopy Stratix family consists of the HC1S25, HC1S30, HC1S40, HC1S60, and HC1S80 devices. Table 1–1 provides the details of the HardCopy Stratix devices.

| Table 1–1. HardCopy Stratix Devices and Features |         |             |            |                 |                |          |

|--------------------------------------------------|---------|-------------|------------|-----------------|----------------|----------|

| Device                                           | LEs (1) | M512 Blocks | M4K Blocks | M-RAM<br>Blocks | DSP Blocks (2) | PLLs (3) |

| HC1S25                                           | 25,660  | 224         | 138        | 2               | 10             | 6        |

| HC1S30                                           | 32,470  | 295         | 171        | 2 (4)           | 12             | 6        |

| HC1S40                                           | 41,250  | 384         | 183        | 2 (4)           | 14             | 6        |

| HC1S60                                           | 57,120  | 574         | 292        | 6               | 18             | 12       |

| HC1S80                                           | 79,040  | 767         | 364        | 6 (4)           | 22             | 12       |

#### *Notes to Table 1–1:*

- (1) LE: logic elements.

- (2) DSP: digital signal processing.

- (3) PLLs: phase-locked loops.

- (4) In HC1S30, HC1S40, and HC1S80 devices, there are fewer M-RAM blocks than in the equivalent Stratix FPGA. All other resources are identical to the Stratix counterpart.

#### **Features**

HardCopy Stratix devices are manufactured on the same 1.5-V, 0.13  $\mu$ m all-layer-copper metal fabrication process (up to eight layers of metal) as the Stratix FPGAs.

- Preserves the functionality of a configured Stratix device

- Pin-compatible with the Stratix counterparts

- On average, 50% faster than their Stratix equivalents

- On average, 40% less power consumption than their Stratix equivalents

- 25,660 to 79,040 LEs

- Up to 5,658,408 RAM bits available

- TriMatrix memory architecture consisting of three RAM block sizes to implement true dual-port memory and first-in-first-out (FIFO) buffers

- Embedded high-speed DSP blocks provide dedicated implementation of multipliers, multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device which provide identical features as the FPGA counterparts, including spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, advanced multiplication, and phase shifting

- Supports numerous single-ended and differential I/O standards

- Supports high-speed networking and communications bus standards including RapidIO<sup>TM</sup>, UTOPIA IV, CSIX, HyperTransport technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

- Supports high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast-cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) megafunctions from Altera<sup>®</sup> MegaCore<sup>®</sup> functions, and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Available in space-saving flip-chip FineLine BGA<sup>®</sup> and wire-bond packages (Tables 1–2 and 1–3)

- Optional emulation of original FPGA configuration sequence

- Optional instant-on power-up

The actual performance and power consumption improvements over the Stratix equivalents mentioned in this data sheet are design-dependent.

| <b>Table 1–2. HardCopy Stratix Device Package Options and I/O Pin Counts</b> <i>Note</i> (1) |                             |                             |                               |  |

|----------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-------------------------------|--|

| Device                                                                                       | 672-Pin<br>FineLine BGA (2) | 780-Pin<br>FineLine BGA (3) | 1,020-Pin<br>FineLine BGA (3) |  |

| HC1S25                                                                                       | 473                         |                             |                               |  |

| HC1S30                                                                                       |                             | 597                         |                               |  |

| HC1S40                                                                                       |                             | 613 <i>(4)</i>              |                               |  |

| HC1S60                                                                                       |                             |                             | 782                           |  |

| HC1S80                                                                                       |                             |                             | 782                           |  |

#### *Notes to Table 1–2:*

- (1) Quartus II I/O pin counts include one additional pin, PLLENA, which is not a general-purpose I/O pin. PLLENA can only be used to enable the PLLs.

- (2) This device uses a wire-bond package.

- (3) This device uses a flip-chip package.

- (4) In the Stratix EP1S40F780 FPGA, the I/O pins U12 and U18 are general-purpose I/O pins. In the FPGA prototype, EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE, and in the HardCopy Stratix HC1S40F780 device, U12 and U18 must be connected to ground. The EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE and HC1S40F780 pin-outs are identical.

| Table 1–3. HardCopy Stratix Device Package Sizes |                         |                         |                           |  |

|--------------------------------------------------|-------------------------|-------------------------|---------------------------|--|

| Device                                           | 672-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA | 1,020-Pin<br>FineLine BGA |  |

| Pitch (mm)                                       | 1.00                    | 1.00                    | 1.00                      |  |

| Area (mm²)                                       | 729                     | 841                     | 1,089                     |  |

| Length × width (mm × mm)                         | 27 × 27                 | 29 × 29                 | 33 × 33                   |  |

# Document Revision History

Table 1–4 shows the revision history for this chapter.

| Table 1–4. Document Revision History |                                                                                                          |                    |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Date and Document<br>Version         | Changes Made                                                                                             | Summary of Changes |  |  |

| September 2008<br>v2.4               | Revised chapter number and metadata.                                                                     | _                  |  |  |

| June 2007 v2.3                       | Updated Introduction section. Updated Table 1–2.                                                         | _                  |  |  |

| December 2006<br>v2.2                | Updated revision history.                                                                                | _                  |  |  |

| March 2006                           | Formerly chapter 5; no content change.                                                                   | _                  |  |  |

| October 2005 v2.1                    | Minor edits                                                                                              | _                  |  |  |

| January 2005 v2.0                    | Minor edits                                                                                              | _                  |  |  |

| June 2003 v1.0                       | Initial release of Chapter 5, Introduction to HardCopy Stratix Devices, in the HardCopy Device Handbook. |                    |  |  |

# 2. Description, Architecture, and Features

H51002-3.4

### Introduction

HardCopy® Stratix® structured ASICs provide a comprehensive alternative to ASICs. The HardCopy Stratix device family is fully supported by the Quartus® II design software, and, combined with a vast intellectual property (IP) portfolio, provides a complete path from prototype to volume production. Designers can now procure devices, tools, and Altera® IP for their high-volume applications.

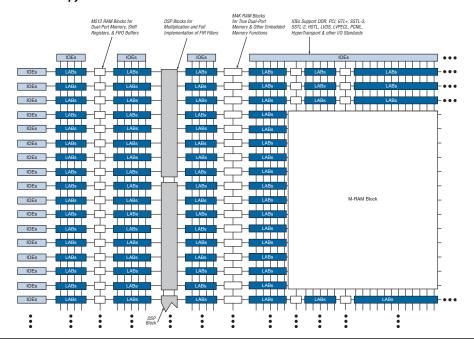

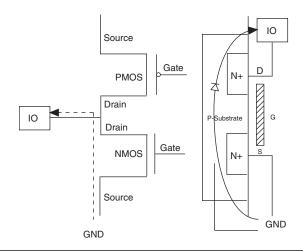

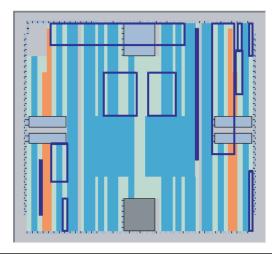

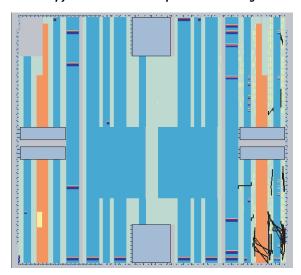

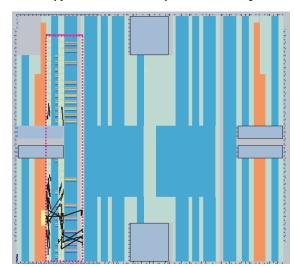

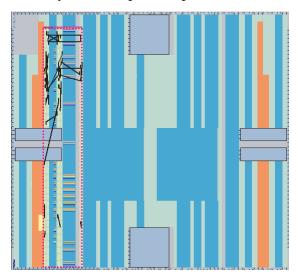

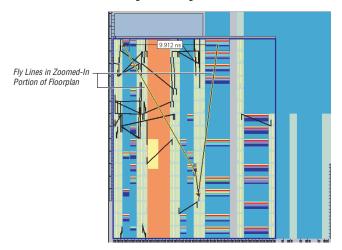

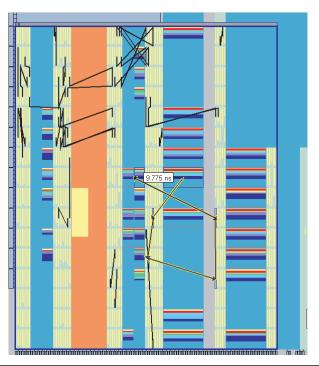

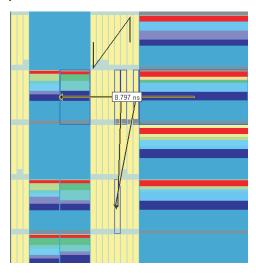

As shown in Figure 2–1, HardCopy Stratix devices preserve their Stratix FPGA counterpart's architecture, but the programmability for logic, memory, and interconnect is removed. HardCopy Stratix devices are also manufactured in the same process technology and process voltage as Stratix FPGAs. Removing all configuration and programmable routing resources and replacing it with direct metal interconnect results in considerable die size reduction and the ensuing cost savings.

Figure 2-1. HardCopy Stratix Device Architecture

The HardCopy Stratix family consists of base arrays that are common to all designs for a particular device density. Design-specific customization is done within the top two metal layers. The base arrays use an area-efficient sea-of-logic-elements (SOLE) core and extend the flexibility of high-density Stratix FPGAs to a cost-effective, high-volume production solution. With a seamless migration process employed in numerous successful designs, functionality-verified Stratix FPGA designs can be migrated to fixed-function HardCopy Stratix devices with minimal risk and guaranteed first-time success.

The SRAM configuration cells of the original Stratix devices are replaced in HardCopy Stratix devices by metal connects, which define the function of each logic element (LE), digital signal processing (DSP) block, phase-locked loop (PLL), embedded memory, and I/O cell in the device. These resources are interconnected using metallization layers. Once a HardCopy Stratix device has been manufactured, the functionality of the device is fixed and no re-programming is possible. However, as is the case with Stratix FPGAs, the PLLs can be dynamically configured in HardCopy Stratix devices.

# HardCopy Stratix and Stratix FPGA Differences

To ensure HardCopy Stratix device functionality and performance, designers should thoroughly test the original Stratix FPGA-based design for satisfactory results before committing the design for migration to a HardCopy Stratix device. Unlike Stratix FPGAs, HardCopy Stratix devices are customized at the time of manufacturing and therefore do not have programmability support.

Since HardCopy Stratix devices are customized within the top two metal layers, no configuration circuitry is required. Refer to "Power-Up Modes in HardCopy Stratix Devices" on page 2–7 for more information.

Depending on the design, HardCopy Stratix devices can provide, on average, a 50% performance improvement over equivalent Stratix FPGAs. The performance improvement is achieved by die size reduction, metal interconnect optimization, and customized signal buffering. HardCopy Stratix devices consume, on average, 40% less power than their equivalent Stratix FPGAs.

Designers can use the Quartus II software to design HardCopy Stratix devices, estimate performance and power consumption, and maximize system throughput.

Table 2–1 illustrates the differences between HardCopy Stratix and Stratix devices.

| Table 2–1. HardCopy Stratix and Stra                                                                                                                        | tix Device Comparison (Part 1 of 2)                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| HardCopy Stratix                                                                                                                                            | Stratix                                                                                                                                   |

| Customized device. All reprogrammability support is removed and no configuration is required.                                                               | Re-programmable with configuration is required upon power-up.                                                                             |

| Average of 50% performance improvement over corresponding FPGA (1).                                                                                         | High-performance FPGA.                                                                                                                    |

| Average of 40% less power consumption compared to corresponding FPGA (1).                                                                                   | Standard FPGA power consumption.                                                                                                          |

| Contact Altera for information regarding specific IP support.                                                                                               | IP support for all devices is available.                                                                                                  |

| Double data rate (DDR) SDRAM maximum operating frequency is pending characterization.                                                                       | DDR SDRAM can operate at 200 MHz for -5 speed grade devices.                                                                              |

| All routing connections are direct and all unused routing is removed.                                                                                       | MultiTrack™ routing stitches together routing resources to provide a path.                                                                |

| HC1S30 and HC1S40 devices have<br>two M-RAM blocks. HC1S80 devices<br>have six M-RAM blocks.                                                                | EP1S30 and EP1S40 devices have four M-RAM blocks. EP1S80 devices have nine M-RAM blocks.                                                  |

| It is not possible to initialize M512 and M4K RAM contents during power-up.                                                                                 | The contents of M512 and M4K RAM blocks can be preloaded during configuration with data specified in a memory initialization file (.mif). |

| The contents of memory output registers are unknown after power-on reset (POR).                                                                             | The contents of memory output registers are initialized to '0' after POR.                                                                 |

| HC1S30 and HC1S40 devices have six PLLs.                                                                                                                    | HC1S30 devices have 10 PLLs.<br>HC1S40 devices have 12 PLLs.                                                                              |

| PLL dynamic reconfiguration uses<br>ROM for information. This<br>reconfiguration is performed in the<br>back-end and does not affect the<br>migration flow. | PLL dynamic reconfiguration uses a MIF to initialize a RAM resource with information.                                                     |

| The I/O elements (IOEs) are equivalent but not identical to FPGA IOEs due to slight design optimizations for HardCopy devices.                              | The IOEs are optimized for the FPGA architecture.                                                                                         |

| Table 2–1. HardCopy Stratix and Stratix Device Comparison (Part 2 of 2)                                                     |                                                                                                                |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| HardCopy Stratix                                                                                                            | Stratix                                                                                                        |  |  |

| The I/O drive strength for single-ended I/O pins are slightly different and is modeled in the HardCopy Stratix IBIS models. | The I/O drive strength for single-ended I/O pins are found in Stratix IBIS models.                             |  |  |

| In the HC1S40 780-pin FineLine BGA® device, the I/O pins U12 and U18 must be connected to ground.                           | In the HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 are available as general-purpose I/O pins. |  |  |

| The BSDL file describes re-ordered Joint Test Action Group (JTAG) boundary-scan chains.                                     | The JTAG boundary-scan chain is defined in the BSDL file.                                                      |  |  |

#### Note to Table 2-1:

(1) Performance and power consumption are design dependant.

## **Logic Elements**

Logic is implemented in HardCopy Stratix devices using the same architectural units as the Stratix device family. The basic unit is the logic element (LE) with logic array blocks (LAB) consisting of 10 LEs. The implementation of LEs and LABs is identical to the Stratix device family.

In the HardCopy Stratix device family, all extraneous routing resources not essential to the specific design are removed for performance and die size efficiency. Therefore, the MultiTrack interconnect for routing implementation between LABs and other device resources in the Stratix device family is no longer necessary in the HardCopy Stratix device family.

Table 2–2 illustrates the differences between HardCopy Stratix and Stratix logic.

| Table 2–2. HardCopy Stratix and Stratix Logic Comparison              |                                                                           |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| HardCopy Stratix Stratix                                              |                                                                           |  |

| All routing connections are direct and all unused routing is removed. | MultiTrack routing stitches routing resources together to provide a path. |  |

## Embedded Memory

TriMatrix™ memory blocks from Stratix devices, including M512, M4K, and M-RAM memory blocks, are available in HardCopy Stratix devices. Embedded memory is seamlessly implemented in the equivalent resource.

Although memory resource implementation is equivalent, the number of specific M-RAM blocks are not necessarily the same between corresponding Stratix and HardCopy Stratix devices. Table 2–3 shows the number of M-RAM blocks available in each device.

| Table 2–3. HardCopy Stratix and Stratix M-RAM Block Comparison |              |         |              |  |

|----------------------------------------------------------------|--------------|---------|--------------|--|

| HardCopy Stratix                                               |              | Stratix |              |  |

| Device                                                         | M-RAM Blocks | Device  | M-RAM Blocks |  |

| HC1S25                                                         | 2            | EP1S25  | 2            |  |

| HC1S30                                                         | 2            | EP1S30  | 4            |  |

| HC1S40                                                         | 2            | EP1S40  | 4            |  |

| HC1S60                                                         | 6            | EP1S60  | 6            |  |

| HC1S830                                                        | 6            | EP1S830 | 9            |  |

In HardCopy Stratix devices, it is not possible to preload RAM contents using a MIF after powering up; the output registers of memory blocks will have unknown values. This occurs because there is no configuration process that is executed.

Violating the setup or hold time requirements on address registers could corrupt the memory contents. This requirement applies to both read and write operations.

Table 2–4 illustrates the differences between HardCopy Stratix and Stratix memory.

| Table 2–4. HardCopy Stratix and Stratix Memory Comparison                                    |                                                                                                             |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| HardCopy Stratix                                                                             | Stratix                                                                                                     |  |  |

| HC1S30 and HC1S40 devices have<br>two M-RAM blocks. HC1S80 devices<br>have six M-RAM blocks. | EP1S30 and EP1S40 devices have four M-RAM blocks. EP1S80 devices have nine M-RAM blocks.                    |  |  |

| It is not possible to initialize M512 and M4k RAM contents during power-up.                  | The contents of M512 and M4K RAM blocks can be preloaded during configuration with data specified in a MIF. |  |  |

| The contents of memory output registers are unknown after POR.                               | The contents of memory output registers are initialized to '0' after POR.                                   |  |  |

### **DSP Blocks**

DSP blocks in HardCopy Stratix devices are architecturally identical to those in Stratix devices. The number of DSP blocks available in HardCopy Stratix devices matches the number of DSP blocks available in the corresponding Stratix device.

## PLLs and Clock Networks

The PLLs in HardCopy Stratix devices are identical to those in Stratix devices. The clock networks are also implemented exactly as they are in Stratix devices. The number of PLLs can vary between corresponding Stratix and HardCopy Stratix devices. Table 2–5 shows the number of PLLs available in each device.

| Table 2–5. HardCopy Stratix and Stratix PLL Comparison |            |         |      |  |

|--------------------------------------------------------|------------|---------|------|--|

| HardCo                                                 | py Stratix | Stra    | ntix |  |

| Device                                                 | PLLs       | Device  | PLLs |  |

| HC1S25                                                 | 6          | EP1S25  | 6    |  |

| HC1S30                                                 | 6          | EP1S30  | 10   |  |

| HC1S40                                                 | 6          | EP1S40  | 12   |  |

| HC1S60                                                 | 12         | EP1S60  | 12   |  |

| EP1S830                                                | 12         | EP1S830 | 12   |  |

Table 2–6 illustrates the differences between HardCopy Stratix and Stratix PLLs.

| Table 2–6. HardCopy Stratix and Stratix PLL Differences                                                                                                     |                                                                                       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| HardCopy Stratix                                                                                                                                            | Stratix                                                                               |  |  |

| HC1S30 and HC1S40 devices have six PLLs.                                                                                                                    | HC1S30 devices have 10 PLLs.<br>HC1S40 devices have12 PLLs.                           |  |  |

| PLL dynamic reconfiguration uses<br>ROM for information. This<br>reconfiguration is performed in the<br>back-end and does not affect the<br>migration flow. | PLL dynamic reconfiguration uses a MIF to initialize a RAM resource with information. |  |  |

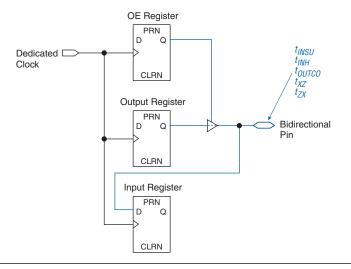

# I/O Structure and Features

The HardCopy Stratix IOEs are equivalent, but not identical to, the Stratix FPGA IOEs. This is due to the reduced die size, layout difference, and metal customization of the HardCopy Stratix device. The differences are minor but may be relevant to customers designing with tight DC and switching characteristics. However, no signal integrity concerns are introduced with HardCopy Stratix IOEs.

When designing with very tight timing constraints (for example, DDR or quad data rate [QDR]), or if using the programmable drive strength option, Altera recommends verifying final drive strength using updated IBIS models located on the Altera website at www.altera.com. Differential I/O standards are unaffected.

I/O pin placement and VREF pin placement rules are identical between HardCopy Stratix and Stratix devices. Unused pin settings will carry over from Stratix device settings and are implemented as tri-stated outputs driving ground or outputs driving  $V_{CC}$ .

In Stratix EP1S40 780-pin FineLine BGA FPGAs, the I/O pins U12 and U18 are available as general-purpose I/O pins. In the FPGA prototype, EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE, and in the Hardcopy Stratix HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 must be connected to ground. HC1S40 780-pin FineLine BGA and EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE pin-outs are identical.

Table 2–7 illustrates the differences between HardCopy Stratix and Stratix I/O pins.

| Table 2–7. HardCopy Stratix and Stratix I/O Pin Comparison                                                                 |                                                                                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| HardCopy Stratix                                                                                                           | Stratix                                                                                                        |  |  |

| The IOEs are equivalent, but not identical to, the FPGA IOEs due to slight design optimizations for HardCopy devices.      | IOEs are optimized for the FPGA architecture.                                                                  |  |  |

| The I/O drive strength for single-ended I/O pins are slightly different and are found in the HardCopy Stratix IBIS models. | The I/O drive strength for single-ended I/O pins are found in Stratix IBIS models.                             |  |  |

| In the HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 must be connected to ground.                           | In the EP1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 are available as general-purpose I/O pins. |  |  |

## Power-Up Modes in HardCopy Stratix Devices

Designers do not need to configure HardCopy Stratix devices, unlike their FPGA counterparts. However, to facilitate seamless migration, configuration can be emulated in HardCopy Stratix devices.

The modes in which a HardCopy Stratix device can be made ready for operation after power-up are: instant on, instant on after 50 ms, and configuration emulation. These modes are briefly described below.

- In instant on mode, the HardCopy Stratix device is available for use shortly after the device receives power. The on-chip POR circuit resets all registers. The CONF\_DONE output is tri-stated once the POR has elapsed. No configuration device or configuration data is necessary.

- In instant on after 50 ms mode, the HardCopy Stratix device performs in a fashion similar to the instant on mode, except that there is an additional delay of 50 ms, during which time the device is held in reset stage. The CONF\_DONE output is pulled low during this time, and then tri-stated after the 50 ms have elapsed. No configuration device or configuration data is necessary for this option.

- In configuration emulation mode, the HardCopy series device emulates the behavior of an APEX or Stratix FPGA during its configuration phase. When this mode is used, the HardCopy device uses a configuration emulation circuit to receive configuration bit streams. When all the configuration data is received, the HardCopy series device transitions into an initialization phase and releases the CONF\_DONE pin to be pulled high. Pulling the CONF\_DONE pin high signals that the HardCopy series device is ready for normal operation. If the optional open-drain INIT\_DONE output is used, the normal operation is delayed until this signal is released by the HardCopy series device.

HardCopy II and some HardCopy Stratix devices do not support configuration emulation mode.

Instant on and instant on after 50 ms modes are the recommended power-up modes because these modes are similar to an ASIC's functionality upon power-up. No changes to the existing board design or the configuration software are required.

All three modes provide significant benefits to system designers. They enable seamless migration of the design from the FPGA device to the HardCopy device with no changes to the existing board design or the configuration software. The pull-up resistors on <code>nCONFIG</code>, <code>nSTATUS</code>, and <code>CONF DONE</code> should be left on the printed circuit board.

For more information, refer to the *HardCopy Series Configuration Emulation* chapter in the *HardCopy Series Handbook*.

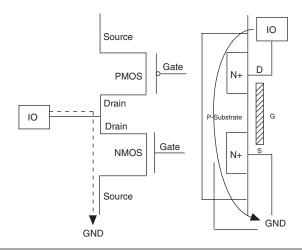

### **Hot Socketing**

HardCopy Stratix devices support hot socketing without any external components. In a hot socketing situation, a device's output buffers are turned off during system power up or power down. To simplify board design, HardCopy Stratix devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$ ). For mixed-voltage environments, you can

drive signals into the device before or during power up or power down without damaging the device. HardCopy Stratix devices do not drive out until they have attained proper operating conditions.

You can power up or power down the  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  pins in any sequence. The power supply ramp rates can range from 100 ns to 100 ms. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF.

- The hot socketing DC specification is  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is  $|I_{IOPIN}| < 8$  mA for 10 ns or less. This specification takes into account the pin capacitance only. Additional capacitance for trace, connector, and loading needs to be taken into consideration separately.  $I_{IOPIN}$  is the current at any user I/O pin on the device.

The DC specification applies when all  $V_{\rm CC}$  supplies to the device are stable in the powered-up or powered-down conditions. For the AC specification, the peak current duration due to power-up transients is 10 ns or less.

## HARDCOPY\_ FPGA\_ PROTOTYPE Devices

HARDCOPY\_FPGA\_PROTOTYPE devices are Stratix FPGAs available for designers to prototype their HardCopy Stratix designs and perform in-system verification before migration to a HardCopy Stratix device. The HARDCOPY\_FPGA\_PROTOTYPE devices have the same available resources as in the final HardCopy Stratix devices.

The Quartus II software version 4.1 and later contains the latest timing models. For designs with tight timing constraints, Altera strongly recommends compiling the design with the Quartus II software version 4.1 or later. To properly verify I/O features, it is important to design with the HARDCOPY\_FPGA\_PROTOTYPE device option prior to migrating to a HardCopy Stratix device.

Some HARDCOPY\_FPGA\_PROTOTYPE devices, as indicated in Table 2–8, have fewer M-RAM blocks compared to the equivalent Stratix FPGAs. The selective removal of these resources provides a significant price benefit to designers using HardCopy Stratix devices.

| Table 2–8. M-RAM Block Comparison Between Various Devices |         |                       |             |               |                 |              |  |

|-----------------------------------------------------------|---------|-----------------------|-------------|---------------|-----------------|--------------|--|

| Number<br>of LEs                                          | _       | GA_PROTOTYPE<br>vices | HardCopy St | ratix Devices | Stratix Devices |              |  |

|                                                           | Device  | M-RAM Blocks          | Device      | M-RAM Blocks  | Device          | M-RAM Blocks |  |

| 25,660                                                    | EP1S25  | 2                     | HC1S25      | 2             | EP1S25          | 2            |  |

| 32,470                                                    | EP1S30  | 2                     | HC1S30      | 2             | EP1S30          | 4            |  |

| 41,250                                                    | EP1S40  | 2                     | HC1S40      | 2             | EP1S40          | 4            |  |

| 57,120                                                    | EP1S60  | 6                     | HC1S60      | 6             | EP1S60          | 6            |  |

| 79,040                                                    | EP1S830 | 6                     | HC1S830     | 6             | EP1S830         | 9            |  |

For more information about how the various features in the Quartus II software can be used for designing HardCopy Stratix devices, refer to the *Quartus II Support for HardCopy Stratix Devices* chapter of the *HardCopy Series Handbook*.

HARDCOPY\_FPGA\_PROTOTYPE FPGA devices have the identical speed grade as the equivalent Stratix FPGAs. However, HardCopy Stratix devices are customized and do not have any speed grading. HardCopy Stratix devices, on an average, can be 50% faster than their equivalent HARDCOPY\_FPGA\_PROTOTYPE devices. The actual improvement is design-dependent.

# Document Revision History

Table 2–9 shows the revision history for this chapter.

| Table 2–9. Document Revision History (Part 1 of 2) |                                                                                                                                            |                    |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Date and Document<br>Version Changes Made          |                                                                                                                                            | Summary of Changes |  |  |

| September 2008<br>v3.4                             | Revised chapter number and metadata.                                                                                                       | _                  |  |  |

| June 2007 v3.3                                     | <ul> <li>Updated Table 2–1.</li> <li>Added note to the "Embedded Memory" section.</li> <li>Updated the "Hot Socketing" section.</li> </ul> | _                  |  |  |

| Table 2–9. Document Revision History (Part 2 of 2) |                                                                                                                                                                                                                                                                         |                    |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Date and Document<br>Version                       | Changes Made                                                                                                                                                                                                                                                            | Summary of Changes |  |  |

| December 2006<br>v3.2                              | Updated revision history.                                                                                                                                                                                                                                               | _                  |  |  |

| March 2006                                         | Formerly chapter 6; no content change.                                                                                                                                                                                                                                  | _                  |  |  |

| October 2005 v3.1                                  | Minor edits     Updated graphics                                                                                                                                                                                                                                        | Minor edits.       |  |  |

| May 2005<br>v3.0                                   | <ul> <li>Added Table 6-1</li> <li>Added the Logic Elements section</li> <li>Added the Embedded Memory section</li> <li>Added the DSP Blocks section</li> <li>Added the PLLs and Clock Networks section</li> <li>Added the I/O Structure and Features section</li> </ul> | Minor update.      |  |  |

| January 2005<br>v2.0                               | Added summary of I/O and timing differences between<br>Stratix FPGAs and HardCopy Stratix devices     Removed section on Quartus II support of HardCopy<br>Stratix devices     Added "Hot Socketing" section                                                            | Minor update.      |  |  |

| August 2003<br>v1.1                                | Edited section headings' hierarchy.                                                                                                                                                                                                                                     | Minor edits.       |  |  |

| June 2003<br>v1.0                                  | Initial release of Chapter 6, Description, Architecture and Features, in the <i>HardCopy Device Handbook</i>                                                                                                                                                            | _                  |  |  |

## 3. Boundary-Scan Support

H51004-3.4

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All HardCopy® Stratix® structured ASICs provide JTAG boundry-scan test (BST) circuitry that complies with the IEEE Std. 1149.1-1990 specification. The BST architecture offers the capability to efficiently test components on printed circuit boards (PCBs) with tight lead spacing by testing pin connections, without using physical test probes, and capturing functional data while a device is in normal operation. Boundary-scan cells in a device can force signals onto pins, or capture data from pin or core logic signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared to expected results.

A device using the JTAG interface uses four required pins, TDI, TDO, TMS, and TCK, and one optional pin, TRST. HardCopy Stratix devices support the JTAG instructions as shown in Table 3-1.

| Table 3–1. HardCop | Table 3–1. HardCopy Stratix JTAG Instructions (Part 1 of 2) |                                                                                                                                                                                                                                    |  |  |  |

|--------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction   | Instruction Code                                            | Description                                                                                                                                                                                                                        |  |  |  |

| SAMPLE/PRELOAD     | 00 0000 0101                                                | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.                                                   |  |  |  |

| EXTEST (1)         | 00 0000 0000                                                | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                |  |  |  |

| BYPASS             | 11 1111 1111                                                | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                        |  |  |  |

| USERCODE           | 00 0000 0111                                                | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                          |  |  |  |

| IDCODE             | 00 0000 0110                                                | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                              |  |  |  |

| HIGHZ (1)          | 00 0000 1011                                                | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins. |  |  |  |

| Table 3–1. HardCopy Stratix JTAG Instructions (Part 2 of 2) |              |                                                                                                                                                                                                                                                                                 |  |  |  |

|-------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction                                            |              |                                                                                                                                                                                                                                                                                 |  |  |  |

| CLAMP (1)                                                   | 00 0000 1010 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |  |  |  |

#### Note to Table 3-1:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

The boundary-scan description language (BSDL) files for HardCopy Stratix devices are different from the corresponding Stratix FPGAs. The BSDL files for HardCopy Stratix devices are available for download from the Altera website at www.altera.com.

The HardCopy Stratix device instruction register length is 10 bits; the USERCODE register length is 32 bits. The USERCODE registers are mask-programmed, so they are not re-programmable. The designer can choose an appropriate 32-bit sequence to program into the USERCODE registers.

Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for HardCopy Stratix devices.

| Table 3–2. HardCopy Stratix Boundary-Scan Register Length |       |  |  |  |

|-----------------------------------------------------------|-------|--|--|--|

| Device Maximum Boundary-Scan Register Length              |       |  |  |  |

| HC1S25 672-pin FineLine BGA                               | 1,458 |  |  |  |

| HC1S30 780-pin FineLine BGA                               | 1,878 |  |  |  |

| HC1S40 780-pin FineLine BGA                               | 1,878 |  |  |  |

| HC1S60 1,020-pin FineLine BGA                             | 2,382 |  |  |  |

| HC1S80 1,020-pin FineLine BGA                             | 2,382 |  |  |  |

|        |                     | IDCODE (32 Bits)         | (1)                                |                    |

|--------|---------------------|--------------------------|------------------------------------|--------------------|

| Device | Version<br>(4 Bits) | Part Number<br>(16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB<br>(1 Bit) (2) |

| HC1S25 | 0000                | 0010 0000 0000 0011      | 000 0110 1110                      | 1                  |

| HC1S30 | 0000                | 0010 0000 0000 0100      | 000 0110 1110                      | 1                  |

| HC1S40 | 0000                | 0010 0000 0000 0101      | 000 0110 1110                      | 1                  |

| HC1S60 | 0000                | 0010 0000 0000 0110      | 000 0110 1110                      | 1                  |

| HC1S80 | 0000                | 0010 0000 0000 0111      | 000 0110 1110                      | 1                  |

#### *Notes to Table 3–3:*

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

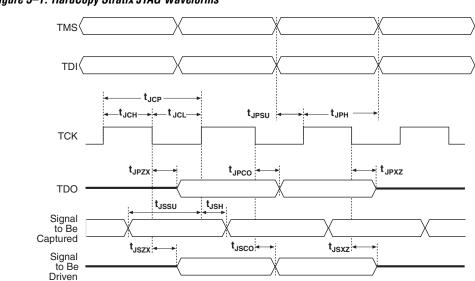

Figure 3–1 shows the timing requirements for the JTAG signals.

Figure 3-1. HardCopy Stratix JTAG Waveforms

Table 3–4 shows the JTAG timing parameters and values for HardCopy Stratix devices.

| Table 3-          | Table 3–4. HardCopy Stratix JTAG Timing Parameters and Values |     |     |      |  |  |

|-------------------|---------------------------------------------------------------|-----|-----|------|--|--|

| Symbol            | Parameter                                                     | Min | Max | Unit |  |  |

| t <sub>JCP</sub>  | TCK clock period                                              | 100 |     | ns   |  |  |

| t <sub>JCH</sub>  | TCK clock high time                                           | 50  |     | ns   |  |  |

| t <sub>JCL</sub>  | TCK clock low time                                            | 50  |     | ns   |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                                          | 20  |     | ns   |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                                           | 45  |     | ns   |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                                     |     | 25  | ns   |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output                      |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance                      |     | 25  | ns   |  |  |

| t <sub>JSSU</sub> | Capture register setup time                                   | 20  |     | ns   |  |  |

| t <sub>JSH</sub>  | Capture register hold time                                    | 45  |     | ns   |  |  |

| t <sub>JSCO</sub> | Update register clock to output                               |     | 35  | ns   |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid output                |     | 35  | ns   |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance                |     | 35  | ns   |  |  |

For more information on JTAG, refer to AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices.

# Document Revision History

Table 3–5 shows the revision history for this chapter.

| Table 3–5. Document Revision History (Part 1 of 2) |                                        |                    |  |  |  |

|----------------------------------------------------|----------------------------------------|--------------------|--|--|--|

| Date and Document<br>Version                       | Changes Made                           | Summary of Changes |  |  |  |

| September 2008<br>v3.4                             | Updated chapter number and metadata.   | _                  |  |  |  |

| June 2007 v3.3                                     | Updated Figure 3–1.                    | _                  |  |  |  |

| December 2006<br>v3.2                              | Updated revision history.              | _                  |  |  |  |

| March 2006                                         | Formerly chapter 7; no content change. | _                  |  |  |  |

| Table 3–5. Document Revision History (Part 2 of 2) |                                                                                         |                    |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--|--|

| Date and Document<br>Version                       | Changes Made                                                                            | Summary of Changes |  |  |

| October 2005 v3.1                                  | Minor edits     Graphic updates                                                         | _                  |  |  |

| May 2005<br>v3.0                                   | Updated "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" section                         |                    |  |  |

| January 2005<br>v2.0                               | Added information about USERCODE registers                                              |                    |  |  |

| June 2003<br>v1.0                                  | Initial release of Chapter 7, Boundary-Scan Support, in the<br>HardCopy Device Handbook |                    |  |  |

### HC1S60F1020N Intel IC FPGA 782 I/O 1020FBGA

HardCopy Series Handbook, Volume 1

## 4. Operating Conditions

H51005-3.4

## Recommended Operating Conditions

Tables 4–1 through 4–3 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.5-V HardCopy® Stratix® devices.

| Table 4-           | Table 4–1. HardCopy Stratix Device Absolute Maximum Ratings       Notes (1), (2) |                         |         |         |      |  |  |

|--------------------|----------------------------------------------------------------------------------|-------------------------|---------|---------|------|--|--|

| Symbol             | Parameter                                                                        | Conditions              | Minimum | Maximum | Unit |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                                   | With respect to ground  | -0.5    | 2.4     | V    |  |  |

| V <sub>CCIO</sub>  |                                                                                  |                         | -0.5    | 4.6     | V    |  |  |

| Vı                 | DC input voltage (3)                                                             |                         | -0.5    | 4.6     | V    |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                                       |                         | -25     | 40      | mA   |  |  |

| T <sub>STG</sub>   | Storage temperature                                                              | No bias                 | -65     | 150     | °C   |  |  |

| T <sub>J</sub>     | Junction temperature                                                             | BGA packages under bias |         | 135     | °C   |  |  |

| Table 4-           | Table 4–2. HardCopy Stratix Device Recommended Operating Conditions |                    |              |                   |      |  |  |

|--------------------|---------------------------------------------------------------------|--------------------|--------------|-------------------|------|--|--|

| Symbol             | Parameter                                                           | Conditions         | Minimum      | Maximum           | Unit |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers                 | (4)                | 1.425        | 1.575             | V    |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation                  | (4), (5)           | 3.00 (3.135) | 3.60 (3.465)      | V    |  |  |

|                    | Supply voltage for output buffers, 2.5-V operation                  | (4)                | 2.375        | 2.625             | V    |  |  |

|                    | Supply voltage for output buffers, 1.8-V operation                  | (4)                | 1.71         | 1.89              | V    |  |  |

|                    | Supply voltage for output buffers, 1.5-V operation                  | (4)                | 1.4          | 1.6               | V    |  |  |

| Vı                 | Input voltage                                                       | (3), (6)           | -0.5         | 4.1               | ٧    |  |  |

| Vo                 | Output voltage                                                      |                    | 0            | V <sub>CCIO</sub> | ٧    |  |  |

| T <sub>J</sub>     | Operating junction temperature                                      | For commercial use | 0            | 85                | °C   |  |  |

|                    |                                                                     | For industrial use | -40          | 100               | °C   |  |  |

| Table 4–3. HardCopy Stratix Device DC Operating Conditions         Note (7) |                                                                                          |                                                      |         |         |         |      |  |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------|---------|---------|---------|------|--|--|

| Symbol                                                                      | Parameter                                                                                | Conditions                                           | Minimum | Typical | Maximum | Unit |  |  |

| I <sub>I</sub>                                                              | Input pin leakage current                                                                | $V_I = V_{CCIOmax}$ to 0 V (8)                       | -10     |         | 10      | μΑ   |  |  |

| l <sub>OZ</sub>                                                             | Tri-stated I/O pin leakage current                                                       | $V_O = V_{CCIOmax}$ to 0 V (8)                       | -10     |         | 10      | μА   |  |  |

| I <sub>CC0</sub>                                                            | V <sub>CC</sub> supply current<br>(standby) (All memory<br>blocks in power-down<br>mode) | V <sub>I</sub> = ground, no load, no toggling inputs |         |         |         | mA   |  |  |

| R <sub>CONF</sub>                                                           | Value of I/O pin pull-up                                                                 | Vi=0; V <sub>CCIO</sub> = 3.3 V (9)                  | 15      | 25      | 50      | kΩ   |  |  |

|                                                                             | resistor before and during configuration                                                 | Vi=0; V <sub>CCIO</sub> = 2.5 V (9)                  | 20      | 45      | 70      | kΩ   |  |  |

|                                                                             | damig comgaration                                                                        | Vi=0; V <sub>CCIO</sub> = 1.8 V (9)                  | 30      | 65      | 100     | kΩ   |  |  |

|                                                                             |                                                                                          | Vi=0; V <sub>CCIO</sub> = 1.5 V (9)                  | 50      | 100     | 150     | kΩ   |  |  |

|                                                                             | Recommended value of I/O pin external pull-down resistor before and during configuration |                                                      |         | 1       | 2       | kΩ   |  |  |

#### *Notes to Tables 4–1 through 4–3:*

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5)  $V_{CCIO}$  maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (7) Typical values are for  $T_A = 25$  °C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power up. This applies for all  $V_{CCIO}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

Tables 4–4 through 4–31 list the DC operating specifications for the supported I/O standards. These tables list minimal specifications only; HardCopy Stratix devices may exceed these specifications. Table 4–32 provides information on capacitance for 1.5-V HardCopy Stratix devices.

| Table 4–4. LVTTL Specifications |                           |                                               |         |         |      |  |

|---------------------------------|---------------------------|-----------------------------------------------|---------|---------|------|--|

| Symbol                          | Parameter                 | Conditions                                    | Minimum | Maximum | Unit |  |

| V <sub>CCIO</sub>               | Output supply voltage     |                                               | 3.0     | 3.6     | V    |  |

| V <sub>IH</sub>                 | High-level input voltage  |                                               | 1.7     | 4.1     | V    |  |

| V <sub>IL</sub>                 | Low-level input voltage   |                                               | -0.5    | 0.7     | V    |  |

| V <sub>OH</sub>                 | High-level output voltage | $I_{OH} = -4 \text{ to } -24 \text{ mA } (1)$ | 2.4     |         | V    |  |

| V <sub>OL</sub>                 | Low-level output voltage  | I <sub>OL</sub> = 4 to 24 mA (1)              |         | 0.45    | V    |  |

| Table 4–5. LVCMOS Specifications |                           |                                                       |                         |         |      |  |

|----------------------------------|---------------------------|-------------------------------------------------------|-------------------------|---------|------|--|

| Symbol                           | Parameter                 | Conditions                                            | Minimum                 | Maximum | Unit |  |

| V <sub>CCIO</sub>                | Output supply voltage     |                                                       | 3.0                     | 3.6     | V    |  |

| V <sub>IH</sub>                  | High-level input voltage  |                                                       | 1.7                     | 4.1     | V    |  |

| V <sub>IL</sub>                  | Low-level input voltage   |                                                       | -0.5                    | 0.7     | V    |  |

| V <sub>OH</sub>                  | High-level output voltage | V <sub>CCIO</sub> = 3.0,<br>I <sub>OH</sub> = -0.1 mA | V <sub>CCIO</sub> - 0.2 |         | V    |  |

| V <sub>OL</sub>                  | Low-level output voltage  | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA  |                         | 0.2     | V    |  |

| Table 4–6. 2.5-V I/O Specifications |                           |                                               |         |         |      |  |

|-------------------------------------|---------------------------|-----------------------------------------------|---------|---------|------|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum | Maximum | Unit |  |

| $V_{\text{CCIO}}$                   | Output supply voltage     |                                               | 2.375   | 2.625   | V    |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                               | 1.7     | 4.1     | V    |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                               | -0.5    | 0.7     | V    |  |

| V <sub>OH</sub>                     | High-level output voltage | I <sub>OH</sub> = -0.1 mA                     | 2.1     |         | V    |  |

|                                     |                           | I <sub>OH</sub> = -1 mA                       | 2.0     |         | V    |  |

|                                     |                           | $I_{OH} = -2 \text{ to } -16 \text{ mA } (1)$ | 1.7     |         | V    |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 0.1 mA                      |         | 0.2     | V    |  |

|                                     |                           | I <sub>OL</sub> = 1 mA                        |         | 0.4     | V    |  |

|                                     |                           | I <sub>OL</sub> = 2 to 16 mA (1)              |         | 0.7     | ٧    |  |

### **Recommended Operating Conditions**

| Table 4-          | Table 4–7. 1.8-V I/O Specifications |                                   |                          |                        |      |  |  |

|-------------------|-------------------------------------|-----------------------------------|--------------------------|------------------------|------|--|--|

| Symbol            | Parameter                           | Conditions                        | Minimum                  | Maximum                | Unit |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                                   | 1.65                     | 1.95                   | ٧    |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                                   | 0.65 × V <sub>CCIO</sub> | 2.25                   | ٧    |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                                   | -0.3                     | $0.35 \times V_{CCIO}$ | V    |  |  |

| V <sub>OH</sub>   | High-level output voltage           | I <sub>OH</sub> = -2 to -8 mA (1) | V <sub>CCIO</sub> - 0.45 |                        | ٧    |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 2 to 8 mA (1)   |                          | 0.45                   | ٧    |  |  |

| Table 4-          | Table 4–8. 1.5-V I/O Specifications |                               |                          |                         |      |  |  |  |

|-------------------|-------------------------------------|-------------------------------|--------------------------|-------------------------|------|--|--|--|

| Symbol            | Parameter                           | Conditions                    | Minimum                  | Maximum                 | Unit |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                               | 1.4                      | 1.6                     | V    |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                               | $0.65 \times V_{CCIO}$   | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                               | -0.3                     | $0.35 \times V_{CCIO}$  | ٧    |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | $I_{OH} = -2 \text{ mA } (1)$ | 0.75 × V <sub>CCIO</sub> |                         | V    |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 2 mA (1)    |                          | $0.25 \times V_{CCIO}$  | V    |  |  |  |

| Table 4–9. 3.3-V LVDS I/O Specifications (Part 1 of 2) |                                  |                                                                                          |         |         |         |      |  |

|--------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------|---------|---------|---------|------|--|

| Symbol                                                 | Parameter                        | Conditions                                                                               | Minimum | Typical | Maximum | Unit |  |

| V <sub>CCIO</sub>                                      | I/O supply voltage               |                                                                                          | 3.135   | 3.3     | 3.465   | V    |  |

| V <sub>ID</sub>                                        | Input differential voltage swing | $0.1 \text{ V} < \text{V}_{\text{CM}} < 1.1 \text{ V}$<br>J = 1  through  10             | 300     |         | 1,000   | mV   |  |

|                                                        |                                  | $1.1 \text{ V} \le \text{V}_{\text{CM}} \le 1.6 \text{ V}$<br>J = 1                      | 200     |         | 1,000   | mV   |  |

|                                                        |                                  | $1.1 \text{ V} \leq \text{V}_{\text{CM}} \leq 1.6 \text{ V}$ $J = 2 \text{ through } 10$ | 100     |         | 1,000   | mV   |  |

|                                                        |                                  | 1.6 V < $V_{CM}$ < 1.8 V<br>J = 1 through 10                                             | 300     |         | 1,000   | mV   |  |

| Table 4-                 | Table 4–9. 3.3-V LVDS I/O Specifications (Part 2 of 2) |                                                                                      |         |         |         |      |  |  |  |

|--------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|

| Symbol                   | Parameter                                              | Conditions                                                                           | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>ICM</sub>         | Input common mode voltage                              | LVDS<br>$0.3 \text{ V} < \text{V}_{\text{ID}} < 1.0 \text{ V}$<br>J = 1  through  10 | 100     |         | 1,100   | mV   |  |  |  |

|                          |                                                        | LVDS<br>0.3 V < V <sub>ID</sub> < 1.0 V<br><i>J</i> = 1 through 10                   | 1,600   |         | 1,800   | mV   |  |  |  |

|                          |                                                        | LVDS<br>0.2 V < V <sub>ID</sub> < 1.0 V<br><i>J</i> = 1                              | 1,100   |         | 1,600   | mV   |  |  |  |

|                          |                                                        | LVDS<br>$0.1 \text{ V} < \text{V}_{\text{ID}} < 1.0 \text{ V}$<br>J = 2  through  10 | 1,100   |         | 1,600   | mV   |  |  |  |

| V <sub>OD</sub> (2)      | Output differential voltage                            | R <sub>L</sub> = 100 Ω                                                               | 250     | 375     | 550     | mV   |  |  |  |

| $\Delta$ V <sub>OD</sub> | Change in V <sub>OD</sub> between high and low         | R <sub>L</sub> = 100 Ω                                                               |         |         | 50      | mV   |  |  |  |

| V <sub>OCM</sub>         | Output common mode voltage                             | R <sub>L</sub> = 100 Ω                                                               | 1,125   | 1,200   | 1,375   | mV   |  |  |  |

| Δ V <sub>OCM</sub>       | Change in V <sub>OCM</sub> between high and low        | R <sub>L</sub> = 100 Ω                                                               |         |         | 50      | mV   |  |  |  |

| R <sub>L</sub>           | Receiver differential input resistor                   |                                                                                      | 90      | 100     | 110     | Ω    |  |  |  |

### **Recommended Operating Conditions**

| Table 4-           | Table 4–10. 3.3-V PCML Specifications           |            |         |                   |         |      |  |  |

|--------------------|-------------------------------------------------|------------|---------|-------------------|---------|------|--|--|

| Symbol             | Parameter                                       | Conditions | Minimum | Typical           | Maximum | Unit |  |  |

| V <sub>CCIO</sub>  | I/O supply voltage                              |            | 3.135   | 3.3               | 3.465   | V    |  |  |

| V <sub>ID</sub>    | Input differential voltage swing                |            | 300     |                   | 600     | mV   |  |  |

| V <sub>ICM</sub>   | Input common mode voltage                       |            | 1.5     |                   | 3.465   | V    |  |  |

| V <sub>OD</sub>    | Output differential voltage                     |            | 300     | 370               | 500     | mV   |  |  |

| ΔV <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low  |            |         |                   | 50      | mV   |  |  |

| V <sub>OCM</sub>   | Output common mode voltage                      |            | 2.5     | 2.85              | 3.3     | V    |  |  |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> between high and low |            |         |                   | 50      | mV   |  |  |

| V <sub>T</sub>     | Output termination voltage                      |            |         | V <sub>CCIO</sub> |         | ٧    |  |  |

| R <sub>1</sub>     | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω    |  |  |

| R <sub>2</sub>     | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω    |  |  |

| Table 4–11. LVPECL Specifications |                                      |                    |         |         |         |        |  |

|-----------------------------------|--------------------------------------|--------------------|---------|---------|---------|--------|--|

| Symbol                            | Parameter                            | Conditions         | Minimum | Typical | Maximum | Unit   |  |

| V <sub>CCIO</sub>                 | I/O supply voltage                   |                    | 3.135   | 3.3     | 3.465   | V      |  |

| V <sub>ID</sub>                   | Input differential voltage swing     |                    | 300     |         | 1,000   | mV     |  |

| V <sub>ICM</sub>                  | Input common mode voltage            |                    | 1       |         | 2       | \<br>\ |  |

| V <sub>OD</sub>                   | Output differential voltage          | $R_L = 100 \Omega$ | 525     | 700     | 970     | mV     |  |