## THE DATASHEET OF FPGA

<u>+00852-56412601</u> <u>(\$\square\$ +00852-56412601</u>

Ounit B, 13/F, Shing Lee Commercial Building No.8 Wing Kut Street, Central HK

### **FLEX 6000**

## Programmable Logic Device Family

March 2001, ver. 4.1 Data Sheet

#### Features...

- Provides an ideal low-cost, programmable alternative to highvolume gate array applications and allows fast design changes during prototyping or design testing

- Product features

- Register-rich, look-up table- (LUT-) based architecture

- OptiFLEX® architecture that increases device area efficiency

- Typical gates ranging from 5,000 to 24,000 gates (see Table 1)

- Built-in low-skew clock distribution tree

- 100% functional testing of all devices; test vectors or scan chains are not required

- System-level features

- In-circuit reconfigurability (ICR) via external configuration device or intelligent controller

- 5.0-V devices are fully compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2*

- Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming additional device logic

- MultiVolt<sup>TM</sup> I/O interface operation, allowing a device to bridge between systems operating at different voltages

- Low power consumption (typical specification less than 0.5 mA in standby mode)

- 3.3-V devices support hot-socketing

| Table 1. FLEX 6000 Device Features   |          |         |          |          |  |  |

|--------------------------------------|----------|---------|----------|----------|--|--|

| Feature                              | EPF6010A | EPF6016 | EPF6016A | EPF6024A |  |  |

| Typical gates (1)                    | 10,000   | 16,000  | 16,000   | 24,000   |  |  |

| Logic elements (LEs)                 | 880      | 1,320   | 1,320    | 1,960    |  |  |

| Maximum I/O pins                     | 102      | 204     | 171      | 218      |  |  |

| Supply voltage (V <sub>CCINT</sub> ) | 3.3 V    | 5.0 V   | 3.3 V    | 3.3 V    |  |  |

#### Note:

(1) The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 14,000 gates in addition to the listed typical gates.

### ...and More Features

- Powerful I/O pins

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Fast path from register to I/O pin for fast clock-to-output time

- Flexible interconnect

- FastTrack<sup>®</sup> Interconnect continuous routing structure for fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fanin logic functions (automatically used by software tools and megafunctions)

- Tri-state emulation that implements internal tri-state networks

- Four low-skew global paths for clock, clear, preset, or logic signals

- Software design support and automatic place-and-route provided by Altera's development system for Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800

- Flexible package options

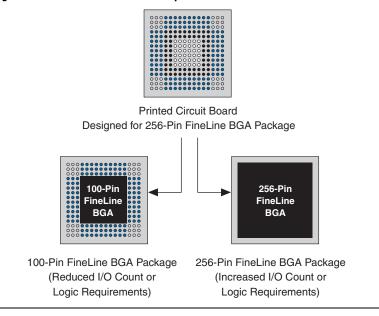

- Available in a variety of packages with 100 to 256 pins, including the innovative FineLine BGA<sup>TM</sup> packages (see Table 2)

- SameFrame<sup>TM</sup> pin-compatibility (with other FLEX® 6000 devices) across device densities and pin counts

- Thin quad flat pack (TQFP), plastic quad flat pack (PQFP), and ball-grid array (BGA) packages (see Table 2)

- Footprint- and pin-compatibility with other FLEX 6000 devices in the same package

- Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, the library of parameterized modules (LPM), Verilog HDL, VHDL, DesignWare components, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, VeriBest, and Viewlogic

| Table 2. Fi | Table 2. FLEX 6000 Package Options & I/O Pin Count |                         |                 |                 |                 |                |                         |  |

|-------------|----------------------------------------------------|-------------------------|-----------------|-----------------|-----------------|----------------|-------------------------|--|

| Device      | 100-Pin<br>TQFP                                    | 100-Pin<br>FineLine BGA | 144-Pin<br>TQFP | 208-Pin<br>PQFP | 240-Pin<br>PQFP | 256-Pin<br>BGA | 256-pin<br>FineLine BGA |  |

| EPF6010A    | 71                                                 |                         | 102             |                 |                 |                |                         |  |

| EPF6016     |                                                    |                         | 117             | 171             | 199             | 204            |                         |  |

| EPF6016A    | 81                                                 | 81                      | 117             | 171             |                 |                | 171                     |  |

| EPF6024A    |                                                    |                         | 117             | 171             | 199             | 218            | 219                     |  |

## General Description

The Altera® FLEX 6000 programmable logic device (PLD) family provides a low-cost alternative to high-volume gate array designs. FLEX 6000 devices are based on the OptiFLEX architecture, which minimizes die size while maintaining high performance and routability. The devices have reconfigurable SRAM elements, which give designers the flexibility to quickly change their designs during prototyping and design testing. Designers can also change functionality during operation via in-circuit reconfiguration.

FLEX 6000 devices are reprogrammable, and they are 100% tested prior to shipment. As a result, designers are not required to generate test vectors for fault coverage purposes, allowing them to focus on simulation and design verification. In addition, the designer does not need to manage inventories of different gate array designs. FLEX 6000 devices are configured on the board for the specific functionality required.

Table 3 shows FLEX 6000 performance for some common designs. All performance values shown were obtained using Synopsys DesignWare or LPM functions. Special design techniques are not required to implement the applications; the designer simply infers or instantiates a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| Application                                | LEs Used |                   | Performance       |                   |     |

|--------------------------------------------|----------|-------------------|-------------------|-------------------|-----|

|                                            |          | -1 Speed<br>Grade | -2 Speed<br>Grade | -3 Speed<br>Grade |     |

| 16-bit loadable counter                    | 16       | 172               | 153               | 133               | MHz |

| 16-bit accumulator                         | 16       | 172               | 153               | 133               | MHz |

| 24-bit accumulator                         | 24       | 136               | 123               | 108               | MHz |

| 16-to-1 multiplexer (pin-to-pin) (1)       | 10       | 12.1              | 13.4              | 16.6              | ns  |

| 16 × 16 multiplier with a 4-stage pipeline | 592      | 84                | 67                | 58                | MHz |

#### Note:

(1) This performance value is measured as a pin-to-pin delay.

Table 4 shows FLEX 6000 performance for more complex designs.

| Application                                                  | LEs Used | Performance       |                   |                   | Units     |

|--------------------------------------------------------------|----------|-------------------|-------------------|-------------------|-----------|

|                                                              |          | -1 Speed<br>Grade | -2 Speed<br>Grade | -3 Speed<br>Grade |           |

| 8-bit, 16-tap parallel finite impulse response (FIR) filter  | 599      | 94                | 80                | 72                | MSPS      |

| 8-bit, 512-point fast Fourier transform (FFT) function       | 1,182    | 75<br>63          | 89<br>53          | 109<br>43         | μS<br>MHz |

| a16450 universal asynchronous<br>receiver/transmitter (UART) | 487      | 36                | 30                | 25                | MHz       |

| PCI bus target with zero wait states                         | 609      | 56                | 49                | 42                | MHz       |

#### Note:

FLEX 6000 devices are supported by Altera development systems; a single, integrated package that offers schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools.

The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the Altera software contains EDA libraries that use device-specific features such as carry chains which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the Altera development systems include DesignWare functions that are optimized for the FLEX 6000 architecture.

The Altera development system runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800.

f See the MAX+PLUS II Programmable Logic Development System & Software Data Sheet and the Quartus Programmable Logic Development System & Software Data Sheet for more information.

<sup>(1)</sup> The applications in this table were created using Altera MegaCore<sup>TM</sup> functions.

## Functional Description

The FLEX 6000 OptiFLEX architecture consists of logic elements (LEs). Each LE includes a 4-input look-up table (LUT), which can implement any 4-input function, a register, and dedicated paths for carry and cascade chain functions. Because each LE contains a register, a design can be easily pipelined without consuming more LEs. The specified gate count for FLEX 6000 devices includes all LUTs and registers.

LEs are combined into groups called logic array blocks (LABs); each LAB contains 10 LEs. The Altera software automatically places related LEs into the same LAB, minimizing the number of required interconnects. Each LAB can implement a medium-sized block of logic, such as a counter or multiplexer.

Signal interconnections within FLEX 6000 devices—and to and from device pins—are provided via the routing structure of the FastTrack Interconnect. The routing structure is a series of fast, continuous row and column channels that run the entire length and width of the device. Any LE or pin can feed or be fed by any other LE or pin via the FastTrack Interconnect. See "FastTrack Interconnect" on page 17 of this data sheet for more information.

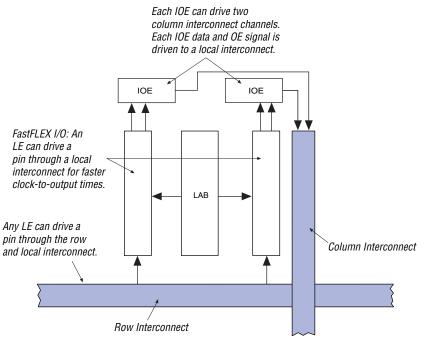

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer. Each IOE is placed next to an LAB, where it can be driven by the local interconnect of that LAB. This feature allows fast clock-to-output times of less than 8 ns when a pin is driven by any of the 10 LEs in the adjacent LAB. Also, any LE can drive any pin via the row and column interconnect. I/O pins can drive the LE registers via the row and column interconnect, providing setup times as low as 2 ns and hold times of 0 ns. IOEs provide a variety of features, such as JTAG BST support, slew-rate control, and tri-state buffers.

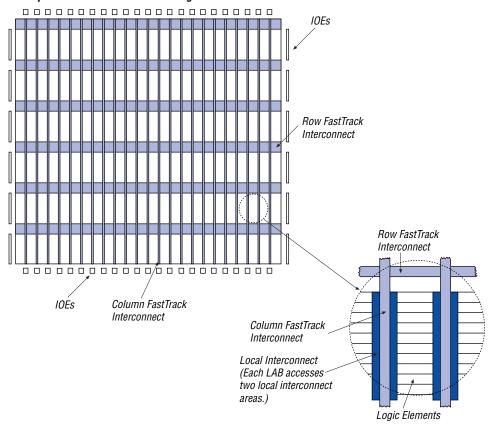

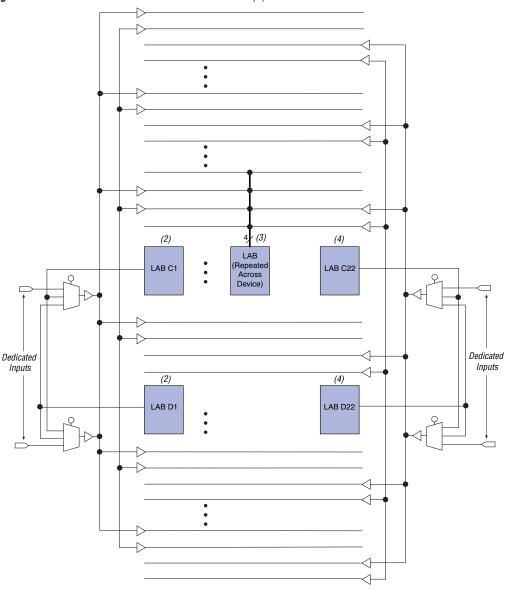

Figure 1 shows a block diagram of the FLEX 6000 OptiFLEX architecture. Each group of ten LEs is combined into an LAB, and the LABs are arranged into rows and columns. The LABs are interconnected by the FastTrack Interconnect. IOEs are located at the end of each FastTrack Interconnect row and column.

Figure 1. OptiFLEX Architecture Block Diagram

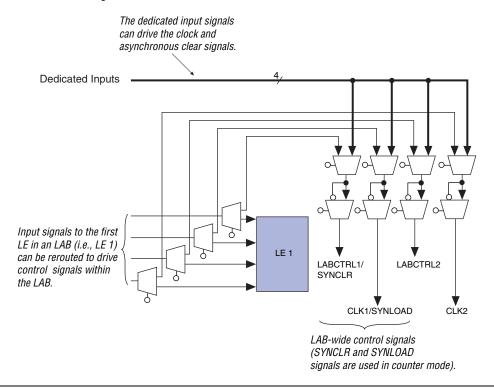

FLEX 6000 devices provide four dedicated, global inputs that drive the control inputs of the flipflops to ensure efficient distribution of high-speed, low-skew control signals. These inputs use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. These inputs can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device. The dedicated global routing structure is built into the device, eliminating the need to create a clock tree.

#### **Logic Array Block**

An LAB consists of ten LEs, their associated carry and cascade chains, the LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure of the FLEX 6000 architecture, and facilitates efficient routing with optimum device utilization and high performance.

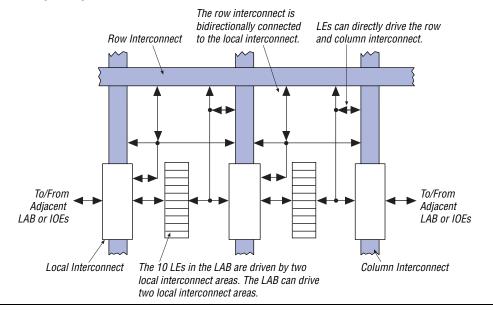

The interleaved LAB structure—an innovative feature of the FLEX 6000 architecture—allows each LAB to drive two local interconnects. This feature minimizes the use of the FastTrack Interconnect, providing higher performance. An LAB can drive 20 LEs in adjacent LABs via the local interconnect, which maximizes fitting flexibility while minimizing die size. See Figure 2.

Figure 2. Logic Array Block

In most designs, the registers only use global clock and clear signals. However, in some cases, other clock or asynchronous clear signals are needed. In addition, counters may also have synchronous clear or load signals. In a design that uses non-global clock and clear signals, inputs from the first LE in an LAB are re-routed to drive the control signals for that LAB. See Figure 3.

Figure 3. LAB Control Signals

#### **Logic Element**

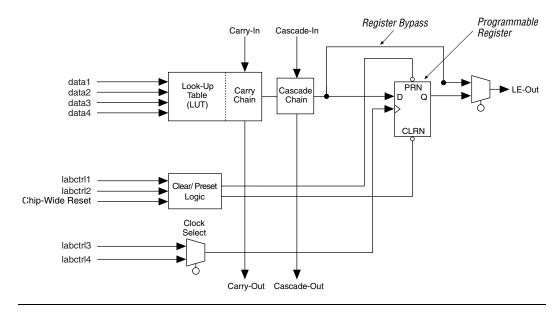

An LE, the smallest unit of logic in the FLEX 6000 architecture, has a compact size that provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. An LE contains a programmable flipflop, carry and cascade chains. Additionally, each LE drives both the local and the FastTrack Interconnect. See Figure 4.

Figure 4. Logic Element

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock and clear control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the outputs of the LE. The LE output can drive both the local interconnect and the FastTrack Interconnect.

The FLEX 6000 architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equivalent comparators with minimum delay. Carry and cascade chains connect LEs 2 through 10 in an LAB and all LABs in the same half of the row. Because extensive use of carry and cascade chains can reduce routing flexibility, these chains should be limited to speed-critical portions of a design.

#### Carry Chain

The carry chain provides a very fast (0.1 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 6000 architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Altera software during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

Because the first LE of each LAB can generate control signals for that LAB, the first LE in each LAB is not included in carry chains. In addition, the inputs of the first LE in each LAB may be used to generate synchronous clear and load enable signals for counters implemented with carry chains.

Carry chains longer than nine LEs are implemented automatically by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from an even-numbered LAB to another even-numbered LAB, or from an odd-numbered LAB to another odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the second LE of the third LAB in the row. In addition, the carry chain does not cross the middle of the row. For instance, in the EPF6016 device, the carry chain stops at the 11th LAB in a row and a new carry chain begins at the 12th LAB.

Figure 5 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. Although the register can be bypassed for simple adders, it can be used for an accumulator function. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the FastTrack Interconnect.

Carry-In Register LUT b1 Carry Chain LE 2 a2 Register LUT Carry Chain LE 3 LUT Register Carry Chain LE *n* + 1 Register Carry-Out LUT Carry Chain LE n + 2

Figure 5. Carry Chain Operation

#### Cascade Chain

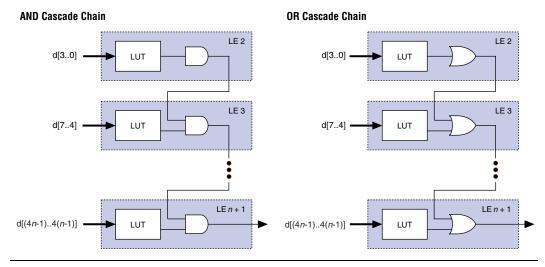

The cascade chain enables the FLEX 6000 architecture to implement very wide fan-in functions. Adjacent LUTs can be used to implement portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR gate (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a delay as low as 0.5 ns per LE. Cascade chain logic can be created automatically by the Altera software during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of cascade chains for the appropriate functions.

A cascade chain implementing an AND gate can use the register in the last LE; a cascade chain implementing an OR gate cannot use this register because of the inversion required to implement the OR gate.

Because the first LE of an LAB can generate control signals for that LAB, the first LE in each LAB is not included in cascade chains. Moreover, cascade chains longer than nine bits are automatically implemented by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from an even-numbered LAB to another even-numbered LAB, or from an odd-numbered LAB to another odd-numbered LAB. For example, the last LE of the first LAB in a row cascades to the second LE of the third LAB. The cascade chain does not cross the center of the row. For example, in an EPF6016 device, the cascade chain stops at the 11th LAB in a row and a new cascade chain begins at the 12th LAB.

Figure 6 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. In this example, functions of 4n variables are implemented with n LEs. The cascade chain requires 3.4 ns to decode a 16-bit address.

Figure 6. Cascade Chain Operation

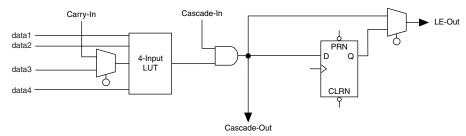

#### LE Operating Modes

The FLEX 6000 LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, synchronous clear, and synchronous load control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions to use an LE operating mode for optimal performance.

Figure 7 shows the LE operating modes.

Figure 7. LE Operating Modes

#### **Normal Mode**

#### **Arithmetic Mode**

#### Notes:

- (1) The register feedback multiplexer is available on LE 2 of each LAB.

- (2) The data1 and data2 input signals can supply a clock enable, up or down control, or register feedback signals for all LEs other than the second LE in an LAB.

- (3) The LAB-wide synchronous clear and LAB-wide synchronous load affect all registers in an LAB.

#### **Normal Mode**

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a 4-input LUT. The Altera software automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal.

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a 3-input function; the other generates a carry output. As shown in Figure 7, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain

The Altera software implements logic functions to use the arithmetic mode automatically where appropriate; the designer does not have to decide how the carry chain will be used.

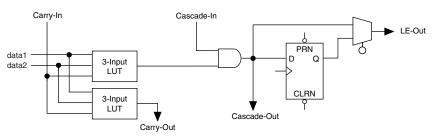

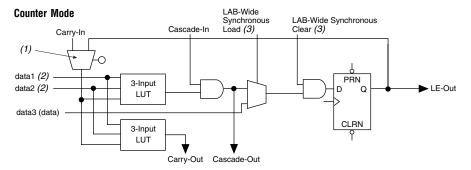

#### **Counter Mode**

The counter mode offers counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in a LAB use counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. In addition, the Altera software automatically places registers that are not in the counter into other LABs.

The counter mode uses two 3-input LUTs: one generates the counter data and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load will override any signal carried on the cascade chain. The synchronous clear overrides the synchronous load.

Either the counter enable or the up/down control may be used for a given counter. Moreover, the synchronous load can be used as a count enable by routing the register output into the data input automatically when requested by the designer.

The second LE of each LAB has a special function for counter mode; the carry-in of the LE can be driven by a fast feedback path from the register. This function gives a faster counter speed for counter carry chains starting in the second LE of an LAB.

The Altera software implements functions to use the counter mode automatically where appropriate. The designer does not have to decide how the carry chain will be used.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-states without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

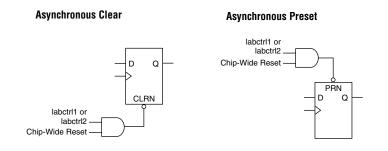

#### Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the LAB-wide signals LABCTRL1 and LABCTRL2. The LE register has an asynchronous clear that can implement an asynchronous preset. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear or preset. Because the clear and preset functions are active-low, the Altera software automatically assigns a logic high to an unused clear or preset signal. The clear and preset logic is implemented in either the asynchronous clear or asynchronous preset mode, which is chosen during design entry (see Figure 8).

Figure 8. LE Clear & Preset Modes

#### Asynchronous Clear

The flipflop can be cleared by either LABCTRL1 or LABCTRL2.

#### **Asynchronous Preset**

An asynchronous preset is implemented with an asynchronous clear. The Altera software provides preset control by using the clear and inverting the input and output of the register. Inversion control is available for the inputs to both LEs and IOEs. Therefore, this technique can be used when a register drives logic or drives a pin.

In addition to the two clear and preset modes, FLEX 6000 devices provide a chip-wide reset pin (DEV\_CLRn) that can reset all registers in the device. The option to use this pin is set in the Altera software before compilation. The chip-wide reset overrides all other control signals. Any register with an asynchronous preset will be preset when the chip-wide reset is asserted because of the inversion technique used to implement the asynchronous preset.

The Altera software can use a programmable NOT-gate push-back technique to emulate simultaneous preset and clear or asynchronous load. However, this technique uses an additional three LEs per register.

#### FastTrack Interconnect

In the FLEX 6000 OptiFLEX architecture, connections between LEs and device I/O pins are provided by the FastTrack Interconnect, a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even for complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

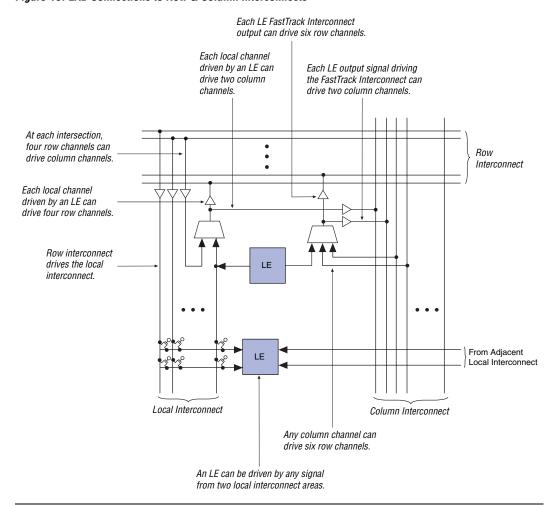

The FastTrack Interconnect consists of column and row interconnect channels that span the entire device. Each row of LABs is served by a dedicated row interconnect, which routes signals between LABs in the same row, and also routes signals from I/O pins to LABs. Additionally, the local interconnect routes signals between LEs in the same LAB and in adjacent LABs. The column interconnect routes signals between rows and routes signals from I/O pins to rows.

LEs 1 through 5 of an LAB drive the local interconnect to the right, while LEs 6 through 10 drive the local interconnect to the left. The DATA1 and DATA3 inputs of each LE are driven by the local interconnect to the left; DATA2 and DATA4 are driven by the local interconnect to the right. The local interconnect also routes signals from LEs to I/O pins. Figure 9 shows an overview of the FLEX 6000 interconnect architecture. LEs in the first and last columns have drivers on both sides so that all LEs in the LAB can drive I/O pins via the local interconnect.

To/From Adjacent LAB

Local Interconnect (32 Channels) (1)

Row Interconnect (n Channels) (1)

Row Interconnect (n Channels) (1)

To/From Adjacent Lab

Column Interconnect (m Channels) (1)

Figure 9. FastTrack Interconnect Architecture

#### Note:

(1) For EPF6010A, EPF6016, and EPF6016A devices, *n* = 144 channels and *m* = 20 channels; for EPF6024A devices, *n* = 186 channels and *m* = 30 channels.

A row channel can be driven by an LE or by one of two column channels. These three signals feed a 3-to-1 multiplexer that connects to six specific row channels. Row channels drive into the local interconnect via multiplexers.

Each column of LABs is served by a dedicated column interconnect. The LEs in an LAB can drive the column interconnect. The LEs in an LAB, a column IOE, or a row interconnect can drive the column interconnect. The column interconnect can then drive another row's interconnect to route the signals to other LABs in the device. A signal from the column interconnect must be routed to the row interconnect before it can enter an LAB.

Each LE has a FastTrack Interconnect output and a local output. The FastTrack interconnect output can drive six row and two column lines directly; the local output drives the local interconnect. Each local interconnect channel driven by an LE can drive four row and two column channels. This feature provides additional flexibility, because each LE can drive any of ten row lines and four column lines.

In addition, LEs can drive global control signals. This feature is useful for distributing internally generated clock, asynchronous clear, and asynchronous preset signals. A pin-driven global signal can also drive data signals, which is useful for high-fan-out data signals.

Each LAB drives two groups of local interconnects, which allows an LE to drive two LABs, or 20 LEs, via the local interconnect. The row-to-local multiplexers are used more efficiently, because the multiplexers can now drive two LABs. Figure 10 shows how an LAB connects to row and column interconnects.

Figure 10. LAB Connections to Row & Column Interconnects

For improved routability, the row interconnect consists of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-length channel, which saves the other half of the channel for the other half of the row. One-third of the row channels are half-length channels.

Table 5 summarizes the FastTrack Interconnect resources available in each FLEX 6000 device.

| Table 5. FLEX 6000 FastTrack Interconnect Resources |      |                     |         |                        |  |  |

|-----------------------------------------------------|------|---------------------|---------|------------------------|--|--|

| Device                                              | Rows | Channels per<br>Row | Columns | Channels per<br>Column |  |  |

| EPF6010A                                            | 4    | 144                 | 22      | 20                     |  |  |

| EPF6016<br>EPF6016A                                 | 6    | 144                 | 22      | 20                     |  |  |

| EPF6024A                                            | 7    | 186                 | 28      | 30                     |  |  |

In addition to general-purpose I/O pins, FLEX 6000 devices have four dedicated input pins that provide low-skew signal distribution across the device. These four inputs can be used for global clock and asynchronous clear control signals. These signals are available as control signals for all LEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device. Using dedicated inputs to route data signals provides a fast path for high fan-out signals.

The local interconnect from LABs located at either end of two rows can drive a global control signal. For instance, in an EPF6016 device, LABs C1, D1, C22, and D22 can all drive global control signals. When an LE drives a global control signal, the dedicated input pin that drives that signal cannot be used. Any LE in the device can drive a global control signal by driving the FastTrack Interconnect into the appropriate LAB. To minimize delay, however, the Altera software places the driving LE in the appropriate LAB. The LE-driving-global signal feature is optimized for speed for control signals; regular data signals are better routed on the FastTrack Interconnect and do not receive any advantage from being routed on global signals. This LE-driving-global control signal feature is controlled by the designer and is not used automatically by the Altera software. See Figure 11.

Figure 11. Global Clock & Clear Distribution Note (1)

#### Notes:

- The global clock and clear distribution signals are shown for EPF6016 and EPF6016A devices. In EPF6010A devices, LABs in rows B and C drive global signals. In EPF6024A devices, LABs in rows C and E drive global signals. The local interconnect from LABs C1 and D1 can drive two global control signals on the left side.

- (2)

- Global signals drive into every LAB as clock, asynchronous clear, preset, and data signals. (3)

- The local interconnect from LABs C22 and D22 can drive two global control signals on the right side.

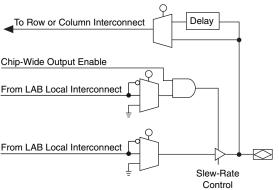

#### I/O Elements

An IOE contains a bidirectional I/O buffer and a tri-state buffer. IOEs can be used as input, output, or bidirectional pins. An IOE receives its data signals from the adjacent local interconnect, which can be driven by a row or column interconnect (allowing any LE in the device to drive the IOE) or by an adjacent LE (allowing fast clock-to-output delays). A FastFLEX<sup>TM</sup> I/O pin is a row or column output pin that receives its data signals from the adjacent local interconnect driven by an adjacent LE. The IOE receives its output enable signal through the same path, allowing individual output enables for every pin and permitting emulation of open-drain buffers. The Altera Compiler uses programmable inversion to invert the data or output enable signals automatically where appropriate. Open-drain emulation is provided by driving the data input low and toggling the OE of each IOE. This emulation is possible because there is one OE per pin.

A chip-wide output enable feature allows the designer to disable all pins of the device by asserting one pin (DEV\_OE). This feature is useful during board debugging or testing.

Figure 12 shows the IOE block diagram.

Figure 12. IOE Block Diagram

Each IOE drives a row or column interconnect when used as an input or bidirectional pin. A row IOE can drive up to six row lines; a column IOE can drive up to two column lines. The input path from the I/O pad to the FastTrack Interconnect has a programmable delay element that can be used to guarantee a zero hold time. Depending on the placement of the IOE relative to what it is driving, the designer may choose to turn on the programmable delay to ensure a zero hold time. Figure 13 shows how an IOE connects to a row interconnect, and Figure 14 shows how an IOE connects to a column interconnect.

Row Interconnect Any LE can drive a pin through the Up to 10 IOEs are on either IOE row and local side of a row. Each IOE can interconnect. drive up to six row LAB channels, and each IOE data and OE signal is driven by IOE the local interconnect. FastFLEX I/O: An LE can drive a pin through the local interconnect for faster clock-to-output times.

Figure 13. IOE Connection to Row Interconnect

Figure 14. IOE Connection to Column Interconnect

## SameFrame Pin-Outs

3.3-V FLEX 6000 devices support the SameFrame pin-out feature for FineLine BGA packages. The SameFrame pin-out feature is the arrangement of balls on FineLine BGA packages such that the lower-ball-count packages form a subset of the higher-ball-count packages. SameFrame pin-outs provide the flexibility to migrate not only from device to device within the same package, but also from one package to another. A given printed circuit board (PCB) layout can support multiple device density/package combinations. For example, a single board layout can support an EPF6016A device in a 100-pin FineLine BGA package or an EPF6024A device in a 256-pin FineLine BGA package.

The Altera software packages provide support to design PCBs with SameFrame pin-out devices. Devices can be defined for present and future use. The Altera software packages generate pin-outs describing how to lay out a board to take advantage of this migration (see Figure 15).

Figure 15. SameFrame Pin-Out Example

Table 6 lists the 3.3-V FLEX 6000 devices with the Same Frame pin-out feature.

| Table 6. 3.3-V FLEX 6000 Devices with SameFrame Pin-Outs |   |   |  |  |  |

|----------------------------------------------------------|---|---|--|--|--|

| Device 100-Pin FineLine BGA 256-Pin FineLine BGA         |   |   |  |  |  |

| EPF6016A                                                 | V | V |  |  |  |

| EPF6024A                                                 |   | V |  |  |  |

# Output Configuration

This section discusses slew-rate control, the MultiVolt I/O interface, power sequencing, and hot-socketing for FLEX 6000 devices.

#### **Slew-Rate Control**

The output buffer in each IOE has an adjustable output slew-rate that can be configured for low-noise or high-speed performance. A slower slew-rate reduces system noise and adds a maximum delay of 6.8 ns. The fast slew-rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew-rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a device-wide basis. The slew-rate setting affects only the falling edge of the output.

#### MultiVolt I/O Interface

The FLEX 6000 device architecture supports the MultiVolt I/O interface feature, which allows FLEX 6000 devices to interface with systems of differing supply voltages. The EPF6016 device can be set for 3.3-V or 5.0-V I/O pin operation. This device has one set of  $V_{CC}$  pins for internal operation and input buffers (VCCINT), and another set for output drivers (VCCIO).

The VCCINT pins on 5.0-V FLEX 6000 devices must always be connected to a 5.0-V power supply. With a 5.0-V  $V_{CCINT}$  level, input voltages are at TTL levels and are therefore compatible with 3.3-V and 5.0-V inputs.

The VCCIO pins on 5.0-V FLEX 6000 devices can be connected to either a 3.3-V or 5.0-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 5.0-V power supply, the output levels are compatible with 5.0-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with VCCIO levels lower than 4.75 V incur a nominally greater timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

On 3.3-V FLEX 6000 devices, the VCCINT pins must be connected to a 3.3-V power supply. Additionally, 3.3-V FLEX 6000A devices can interface with 2.5-V, 3.3-V, or 5.0-V systems when the VCCIO pins are tied to 2.5 V. The output can drive 2.5-V systems, and the inputs can be driven by 2.5-V, 3.3-V, or 5.0-V systems. When the VCCIO pins are tied to 3.3 V, the output can drive 3.3-V or 5.0-V systems. MultiVolt I/Os are not supported on 100-pin TQFP or 100-pin FineLine BGA packages.

| Table 7 describes FLEX 6000 MultiVolt I/O sup | port. |

|-----------------------------------------------|-------|

|-----------------------------------------------|-------|

| Table 7. FLEX 6000 MultiVolt I/O Support |                   |     |                  |     |       |                   |     |  |

|------------------------------------------|-------------------|-----|------------------|-----|-------|-------------------|-----|--|

| V <sub>CCINT</sub>                       | V <sub>CCIO</sub> | Inp | Input Signal (V) |     |       | Output Signal (V) |     |  |

| (V)                                      | (V)               | 2.5 | 3.3              | 5.0 | 2.5   | 3.3               | 5.0 |  |

| 3.3                                      | 2.5               | v   | v                | V   | V     |                   |     |  |

| 3.3                                      | 3.3               | v   | v                | v   | v (1) | v                 | v   |  |

| 5.0                                      | 3.3               |     | v                | v   |       | v                 | v   |  |

| 5.0                                      | 5.0               |     | v                | v   |       |                   | v   |  |

#### Note

(1) When  $V_{\rm CCIO} = 3.3$  V, a FLEX 6000 device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on 5.0-V or 3.3-V FLEX 6000 devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the open-drain pin is active, it will drive low. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{\rm OL}$  current specification should be considered when selecting a pull-up resistor.

Output pins on 5.0-V FLEX 6000 devices with  $V_{CCIO}$  = 3.3 V or 5.0 V (with a pull-up resistor to the 5.0-V supply) can also drive 5.0-V CMOS input pins. In this case, the pull-up transistor will turn off when the pin voltage exceeds 3.3 V. Therefore, the pin does not have to be open-drain.

#### **Power Sequencing & Hot-Socketing**

Because FLEX 6000 family devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $\rm V_{CCIO}$  and  $\rm V_{CCINT}$  power planes can be powered in any order.

Signals can be driven into 3.3-V FLEX 6000 devices before and during power up without damaging the device. Additionally, FLEX 6000 devices do not drive out during power up. Once operating conditions are reached, FLEX 6000 devices operate as specified by the user.

### IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All FLEX 6000 devices provide JTAG BST circuitry that comply with the IEEE Std. 1149.1-1990 specification. Table 8 shows JTAG instructions for FLEX 6000 devices. JTAG BST can be performed before or after configuration, but not during configuration (except when you disable JTAG support in user mode).

1 See Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices) for more information on JTAG BST circuitry.

| Table 8. FLEX 6000 JTAG Instructions |                                                                                                                                                                                                |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction                     | Description                                                                                                                                                                                    |  |  |  |

| SAMPLE/PRELOAD                       | Allows a snapshot of the signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.           |  |  |  |

| EXTEST                               | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test result at the input pins.                          |  |  |  |

| BYPASS                               | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through the selected device to adjacent devices during normal device operation. |  |  |  |

The instruction register length for FLEX 6000 devices is three bits. Table 9 shows the boundary-scan register length for FLEX 6000 devices.

| Table 9. FLEX 6000 Device Boundary-Scan Register Length |                               |  |  |  |

|---------------------------------------------------------|-------------------------------|--|--|--|

| Device                                                  | Boundary-Scan Register Length |  |  |  |

| EPF6010A                                                | 522                           |  |  |  |

| EPF6016                                                 | 621                           |  |  |  |

| EPF6016A                                                | 522                           |  |  |  |

| EPF6024A                                                | 666                           |  |  |  |

FLEX 6000 devices include a weak pull-up on JTAG pins.

f See Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices) for more information.

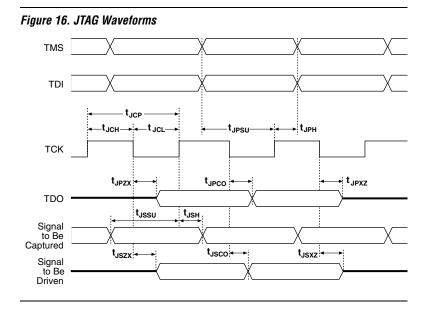

Figure 16 shows the timing requirements for the JTAG signals.

Table 10 shows the JTAG timing parameters and values for FLEX 6000 devices.

| Table 1           | Table 10. JTAG Timing Parameters & Values      |     |     |      |  |  |  |

|-------------------|------------------------------------------------|-----|-----|------|--|--|--|

| Symbol            | Parameter                                      | Min | Max | Unit |  |  |  |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |  |  |  |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |  |  |  |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |  |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |  |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |  |  |  |

| t <sub>JPCO</sub> | JTAG port clock-to-output                      |     | 25  | ns   |  |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |  |  |  |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |  |  |  |

| t <sub>JSCO</sub> | Update register clock-to-output                |     | 35  | ns   |  |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid        |     | 35  | ns   |  |  |  |

|                   | output                                         |     |     |      |  |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |  |  |  |

### **Generic Testing**

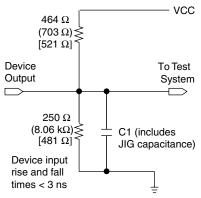

Each FLEX 6000 device is functionally tested. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% configuration yield. AC test measurements for FLEX 6000 devices are made under conditions equivalent to those shown in Figure 17. Multiple test patterns can be used to configure devices during all stages of the production flow.

#### Figure 17. AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers without parentheses are for 5.0-V devices or outputs. Numbers in parentheses are for 3.3-V devices or outputs. Numbers in brackets are for 2.5-V devices or outputs.

# Operating Conditions

Tables 11 through 18 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for 5.0-V and 3.3-V FLEX 6000 devices.

| Table 11. FLEX 6000 5.0-V Device Absolute Maximum Ratings Note (1) |                            |                              |      |     |      |  |

|--------------------------------------------------------------------|----------------------------|------------------------------|------|-----|------|--|

| Symbol                                                             | Parameter                  | Conditions                   | Min  | Max | Unit |  |

| V <sub>CC</sub>                                                    | Supply voltage             | With respect to ground (2)   | -2.0 | 7.0 | ٧    |  |

| V <sub>I</sub>                                                     | DC input voltage           |                              | -2.0 | 7.0 | V    |  |

| I <sub>OUT</sub>                                                   | DC output current, per pin |                              | -25  | 25  | mA   |  |

| T <sub>STG</sub>                                                   | Storage temperature        | No bias                      | -65  | 150 | ° C  |  |

| T <sub>AMB</sub>                                                   | Ambient temperature        | Under bias                   | -65  | 135 | ° C  |  |

| TJ                                                                 | Junction temperature       | PQFP, TQFP, and BGA packages |      | 135 | ° C  |  |

| Symbol             | Parameter                                           | Conditions         | Min         | Max                      | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|--------------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 5.0-V operation  | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | ٧    |

|                    | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)              | ٧    |

| VI                 | Input voltage                                       |                    | -0.5        | V <sub>CCINT</sub> + 0.5 | ٧    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub>        | ٧    |

| TJ                 | Operating temperature                               | For commercial use | 0           | 85                       | ° C  |

|                    |                                                     | For industrial use | -40         | 100                      | ° C  |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                       | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                       | ns   |

| Table 1          | Table 13. FLEX 6000 5.0-V Device DC Operating ConditionsNotes (5), (6) |                                                              |                         |     |                          |      |  |  |

|------------------|------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----|--------------------------|------|--|--|

| Symbol           | Parameter                                                              | Conditions                                                   | Min                     | Тур | Max                      | Unit |  |  |

| V <sub>IH</sub>  | High-level input voltage                                               |                                                              | 2.0                     |     | V <sub>CCINT</sub> + 0.5 | ٧    |  |  |

| V <sub>IL</sub>  | Low-level input voltage                                                |                                                              | -0.5                    |     | 0.8                      | V    |  |  |

| V <sub>OH</sub>  | 5.0-V high-level TTL output voltage                                    | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 4.75 \text{ V } (7)$  | 2.4                     |     |                          | ٧    |  |  |

|                  | 3.3-V high-level TTL output voltage                                    | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)   | 2.4                     |     |                          | ٧    |  |  |

|                  | 3.3-V high-level CMOS output voltage                                   | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7) | V <sub>CCIO</sub> - 0.2 |     |                          | ٧    |  |  |

| V <sub>OL</sub>  | 5.0-V low-level TTL output voltage                                     | $I_{OL}$ = 8 mA DC, $V_{CCIO}$ = 4.75 V (8)                  |                         |     | 0.45                     | ٧    |  |  |

|                  | 3.3-V low-level TTL output voltage                                     | $I_{OL}$ = 8 mA DC, $V_{CCIO}$ = 3.00 V (8)                  |                         |     | 0.45                     | ٧    |  |  |

|                  | 3.3-V low-level CMOS output voltage                                    | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ |                         |     | 0.2                      | ٧    |  |  |

| I <sub>I</sub>   | Input pin leakage current                                              | V <sub>I</sub> = V <sub>CC</sub> or ground (8)               | -10                     |     | 10                       | μΑ   |  |  |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current                                     | $V_O = V_{CC}$ or ground (8)                                 | -40                     |     | 40                       | μΑ   |  |  |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby)                               | V <sub>I</sub> = ground, no load                             |                         | 0.5 | 5                        | mA   |  |  |

| Table 14. FLEX 6000 5.0-V Device CapacitanceNote (9) |                                       |                                     |     |     |      |  |  |

|------------------------------------------------------|---------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                               | Parameter                             | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                      | Input capacitance for I/O pin         | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| C <sub>INCLK</sub>                                   | Input capacitance for dedicated input | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                     | Output capacitance                    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- $Minimum\ DC\ input\ is\ -0.5\ V.\ During\ transitions,\ the\ inputs\ may\ undershoot\ to\ -2.0\ V\ or\ overshoot\ to\ 7.0\ V\ for\ overshoot\ to\ -2.0\ V\ overshoot\ -2.0\ v\ overshoot\ to\ -2.0\ v\ overshoot\ -2.0\ overs$ input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time to 100 ms. V<sub>CC</sub> must rise monotonically.

(5) Typical values are for T<sub>A</sub> = 25° C and V<sub>CC</sub> = 5.0 V.

(6) These values are specified under the FLEX 6000 Recommended Operating Conditions shown in Table 12 on page 31. The  $I_{\mathrm{OH}}$  parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) Capacitance is sample-tested only.

| Table 15. FLEX 6000 3.3-V Device Absolute Maximum Ratings Note (1) |                            |                              |      |      |      |  |  |

|--------------------------------------------------------------------|----------------------------|------------------------------|------|------|------|--|--|

| Symbol                                                             | Parameter                  | Conditions                   | Min  | Max  | Unit |  |  |

| V <sub>CC</sub>                                                    | Supply voltage             | With respect to ground (2)   | -0.5 | 4.6  | V    |  |  |

| VI                                                                 | DC input voltage           |                              | -2.0 | 5.75 | ٧    |  |  |

| I <sub>OUT</sub>                                                   | DC output current, per pin |                              | -25  | 25   | mA   |  |  |

| T <sub>STG</sub>                                                   | Storage temperature        | No bias                      | -65  | 150  | ° C  |  |  |

| T <sub>AMB</sub>                                                   | Ambient temperature        | Under bias                   | -65  | 135  | °C   |  |  |

| TJ                                                                 | Junction temperature       | PQFP, PLCC, and BGA packages |      | 135  | ° C  |  |  |

| Symbol             | Parameter                                           | Conditions         | Min         | Max               | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|-------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | ٧    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | ٧    |

|                    | Supply voltage for output buffers, 2.5-V operation  | (3), (4)           | 2.30 (2.30) | 2.70 (2.70)       | ٧    |

| VI                 | Input voltage                                       |                    | -0.5        | 5.75              | V    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub> | V    |

| T <sub>J</sub>     | Operating temperature                               | For commercial use | 0           | 85                | °C   |

|                    |                                                     | For industrial use | -40         | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                | ns   |

| Symbol           | Parameter                                | Conditions                                                   | Min                     | Тур | Max  | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                              | 1.7                     |     | 5.75 | ٧    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                              | -0.5                    |     | 0.8  | ٧    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)   | 2.4                     |     |      | ٧    |

|                  | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7) | V <sub>CCIO</sub> - 0.2 |     |      | V    |

|                  | 2.5-V high-level output voltage          | $I_{OH} = -100 \mu A DC, V_{CCIO} = 2.30 V (7)$              | 2.1                     |     |      | V    |

|                  |                                          | I <sub>OH</sub> = -1 mA DC, V <sub>CCIO</sub> = 2.30 V (7)   | 2.0                     |     |      | V    |

|                  |                                          | $I_{OH} = -2 \text{ mA DC}, V_{CCIO} = 2.30 \text{ V}$ (7)   | 1.7                     |     |      | V    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | $I_{OL} = 8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$   |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ |                         |     | 0.2  | ٧    |

|                  | 2.5-V low-level output voltage           | I <sub>OL</sub> = 100 μA DC, V <sub>CCIO</sub> = 2.30 V (8)  |                         |     | 0.2  | V    |

|                  |                                          | I <sub>OL</sub> = 1 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.4  | V    |

|                  |                                          | I <sub>OL</sub> = 2 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.7  | V    |

| l <sub>l</sub>   | Input pin leakage current                | V <sub>I</sub> = 5.3 V to ground (8)                         | -10                     |     | 10   | μΑ   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | V <sub>O</sub> = 5.3 V to ground (8)                         | -10                     |     | 10   | μΑ   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load                             |                         | 0.5 | 5    | mA   |

| Table 18. FLEX 6000 3.3-V Device CapacitanceNote (9) |                                       |                                     |     |     |      |  |  |

|------------------------------------------------------|---------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                               | Parameter                             | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                      | Input capacitance for I/O pin         | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| C <sub>INCLK</sub>                                   | Input capacitance for dedicated input | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                     | Output capacitance                    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) The minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms. V<sub>CC</sub> must rise monotonically.

(5) Typical values are for T<sub>A</sub> = 25° C and V<sub>CC</sub> = 3.3 V.

(6) These values are specified under Table 16 on page 33.

(7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) Capacitance is sample-tested only.

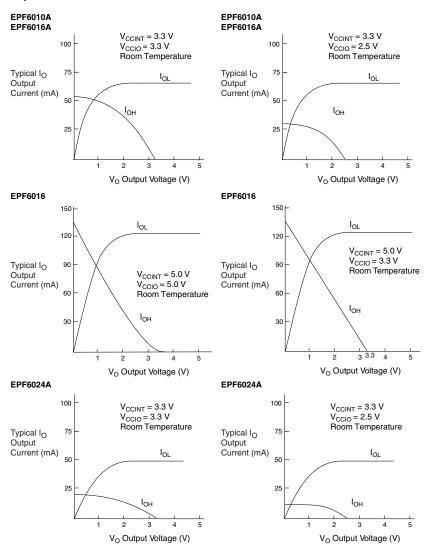

Figure 18 shows the typical output drive characteristics of 5.0-V and 3.3-V FLEX 6000 devices with 5.0-V, 3.3-V, and 2.5-V  $V_{\rm CCIO}$ . When  $V_{\rm CCIO}$  = 5.0 V on EPF6016 devices, the output driver is compliant with the *PCI Local Bus Specification, Revision* 2.2 for 5.0-V operation. When  $V_{\rm CCIO}$  = 3.3 V on the EPF6010A and EPF6016A devices, the output driver is compliant with the *PCI Local Bus Specification, Revision* 2.2 for 3.3-V operation.

Figure 18. Output Drive Characteristics

### **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay ( $t_{CO} + t_{REG\_TO\_OUT}$ )

- Routing delay  $(t_{ROW} + t_{LOCAL})$

- LE LUT delay ( $t_{DATA\_TO\_REG}$ )

- LE register setup time  $(t_{SU})$

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

Timing simulation and delay prediction are available with the Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

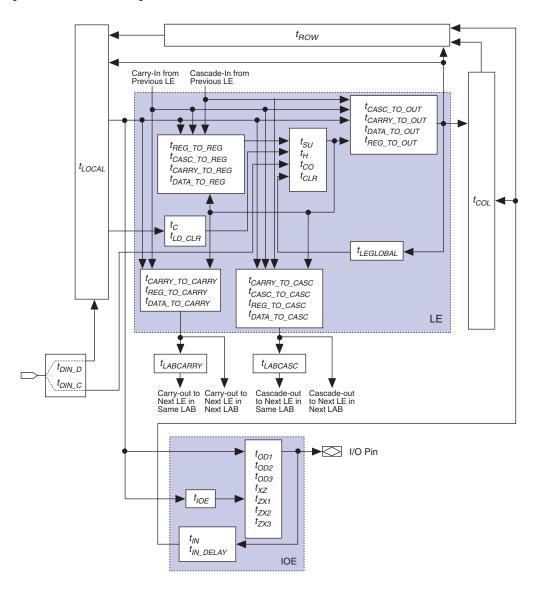

Figure 19 shows the overall timing model, which maps the possible routing paths to and from the various elements of the FLEX 6000 device.

Figure 19. FLEX 6000 Timing Model

Tables 19 through 21 describe the FLEX 6000 internal timing microparameters, which are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and timing analysis. Tables 22 and 23 describe FLEX 6000 external timing parameters.

| Symbol                      | Parameter                                                                               | Conditions |

|-----------------------------|-----------------------------------------------------------------------------------------|------------|

| t <sub>REG_TO_REG</sub>     | LUT delay for LE register feedback in carry chain                                       |            |

| t <sub>CASC_TO_REG</sub>    | Cascade-in to register delay                                                            |            |

| t <sub>CARRY_TO_REG</sub>   | Carry-in to register delay                                                              |            |

| t <sub>DATA_TO_REG</sub>    | LE input to register delay                                                              |            |

| t <sub>CASC_TO_OUT</sub>    | Cascade-in to LE output delay                                                           |            |

| t <sub>CARRY_TO_OUT</sub>   | Carry-in to LE output delay                                                             |            |

| t <sub>DATA_TO_OUT</sub>    | LE input to LE output delay                                                             |            |

| t <sub>REG_TO_OUT</sub>     | Register output to LE output delay                                                      |            |

| t <sub>SU</sub>             | LE register setup time before clock; LE register recovery time after asynchronous clear |            |

| t <sub>H</sub>              | LE register hold time after clock                                                       |            |

| $t_{CO}$                    | LE register clock-to-output delay                                                       |            |

| t <sub>CLR</sub>            | LE register clear delay                                                                 |            |

| $t_C$                       | LE register control signal delay                                                        |            |

| t <sub>LD_CLR</sub>         | Synchronous load or clear delay in counter mode                                         |            |

| t <sub>CARRY_TO_CARRY</sub> | Carry-in to carry-out delay                                                             |            |

| t <sub>REG_TO_CARRY</sub>   | Register output to carry-out delay                                                      |            |

| t <sub>DATA_TO_CARRY</sub>  | LE input to carry-out delay                                                             |            |

| t <sub>CARRY_TO_CASC</sub>  | Carry-in to cascade-out delay                                                           |            |

| t <sub>CASC_TO_CASC</sub>   | Cascade-in to cascade-out delay                                                         |            |

| t <sub>REG_TO_CASC</sub>    | Register-out to cascade-out delay                                                       |            |

| t <sub>DATA_TO_CASC</sub>   | LE input to cascade-out delay                                                           |            |

| t <sub>CH</sub>             | LE register clock high time                                                             |            |

| $t_{CL}$                    | LE register clock low time                                                              |            |

|                             | +                                                                                       | _          |

| Table 20. 10          | E Timing Microparameters Note (1)                                                         |                |

|-----------------------|-------------------------------------------------------------------------------------------|----------------|

| Symbol                | Parameter                                                                                 | Conditions     |

| t <sub>OD1</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub> | C1 = 35 pF (2) |

| t <sub>OD2</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage        | C1 = 35 pF (3) |

| t <sub>OD3</sub>      | Output buffer and pad delay, slow slew rate = on                                          | C1 = 35 pF (4) |

| $t_{XZ}$              | Output buffer disable delay                                                               | C1 = 5 pF      |

| t <sub>ZX1</sub>      | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub>  | C1 = 35 pF (2) |

| t <sub>ZX2</sub>      | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage         | C1 = 35 pF (3) |

| $t_{ZX3}$             | IOE output buffer enable delay, slow slew rate = on                                       | C1 = 35 pF (4) |

| t <sub>IOE</sub>      | Output enable control delay                                                               |                |

| t <sub>IN</sub>       | Input pad and buffer to FastTrack Interconnect delay                                      |                |

| t <sub>IN_DELAY</sub> | Input pad and buffer to FastTrack Interconnect delay with additional delay turned on      |                |

| Symbol                | Parameter                                                                                                            | Conditions |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| t <sub>LOCAL</sub>    | LAB local interconnect delay                                                                                         |            |

| t <sub>ROW</sub>      | Row interconnect routing delay                                                                                       | (5)        |

| t <sub>COL</sub>      | Column interconnect routing delay                                                                                    | (5)        |

| t <sub>DIN_D</sub>    | Dedicated input to LE data delay                                                                                     | (5)        |

| t <sub>DIN_C</sub>    | Dedicated input to LE control delay                                                                                  |            |

| t <sub>LEGLOBAL</sub> | LE output to LE control via internally-generated global signal delay                                                 | (5)        |

| t <sub>LABCARRY</sub> | Routing delay for the carry-out of an LE driving the carry-in signal of a different LE in a different LAB            |            |

| t <sub>LABCASC</sub>  | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |

| Table 22. Ex     | ternal Reference Timing Parameters                                                   |            |

|------------------|--------------------------------------------------------------------------------------|------------|

| Symbol           | Parameter                                                                            | Conditions |

| t <sub>1</sub>   | Register-to-register test pattern                                                    | (6)        |

| t <sub>DRR</sub> | Register-to-register delay via 4 LEs, 3 row interconnects, and 4 local interconnects | (7)        |

| Table 23. Ex      | ternal Timing Parameters                                                        |            |

|-------------------|---------------------------------------------------------------------------------|------------|

| Symbol            | Parameter                                                                       | Conditions |

| t <sub>INSU</sub> | Setup time with global clock at LE register                                     | (8)        |

| t <sub>INH</sub>  | Hold time with global clock at LE register                                      | (8)        |

| tоитсо            | Clock-to-output delay with global clock with LE register using FastFLEX I/O pin | (8)        |

#### Notes to tables:

- Microparameters are timing delays contributed by individual architectural elements and cannot be measured explicitly.

- (2) Operating conditions:

- $\hat{V_{CCIO}} = \widecheck{5}.0~V \pm 5\%$  for commercial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO}$  = 5.0 V  $\pm 10\%$  for industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO}$  = 3.3 V ±10% for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (3) Operating conditions:

- $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO}$  = 2.5 V ±0.2 V for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (4) Operating conditions:

- $V_{CCIO} = 2.5 \text{ V}, 3.3 \text{ V}, \text{ or } 5.0 \text{ V}.$

- (5) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (6) This timing parameter shows the delay of a register-to-register test pattern and is used to determine speed grades. There are 12 LEs, including source and destination registers. The row and column interconnects between the registers vary in length.

- (7) This timing parameter is shown for reference and is specified by characterization.

- (8) This timing parameter is specified by characterization.

Tables 24 through 28 show the timing information for EPF6010A and EPF6016A devices.

| Parameter                 |     |     | Speed | Grade |     |     | Unit |

|---------------------------|-----|-----|-------|-------|-----|-----|------|

|                           | -1  |     | -2    |       | -3  |     | 1    |

|                           | Min | Max | Min   | Max   | Min | Max |      |